# **Vapor Phase Doping of Boron in Silicon**

Kai Zang

Mentor: Maurice Stevens, Ted Berg, Prof. Ted Kamins

EE 412 Final Report, Spring 2015

#### Abstract

In this report I will demonstrate a working recipe to dope boron directly into Si using RPCVD (epi2). I will also demonstrate simulation based on literature review that matched experiment results. This work will enable users in SNF to dope boron into silicon as an alternative to ion implantation and use simulation code to manipulate doping profile.

#### **Motivation & Introduction**

For the past years, Stanford Nanofabrication Facilities (SNF) has developed recipes to dope boron or phosphor into Silicon. It is done in gas-phase doping furnaces where temperature controlled bubblers go through BBr<sub>3</sub> (as a boron source) or PoCl<sub>3</sub> (as phosphorous source). The doping is split into two phases, pre-deposition and annealing with the following reactions.

$$4POCl_3 + 3O_2 \rightarrow 2P_2O_5 + 6Cl_2$$

$$2P_2O_5 + 5Si \leftrightarrow 4P + 5SiO_2$$

In this process, users need to use Buffered Oxide Etch (BOE) to etch away Silicon oxide on surface. This process works very well as phosphor-rich glass is easy to remove.

However, problem happens for boron dope furnace. From its reaction below, users also need to remove silicon oxide on surface, yet boron-rich glass is extremely difficult to remove.

$$4BBr_3 + 3O_2 \rightarrow 2B_2O_3 + 6Br_2$$

$2B_2O_3 + 3Si \leftrightarrow 4B + 3SiO_2$

An alternative to doping Si with boron without epitaxy growth would be ion implantation. It has many advantages including precise control of dose and depth profile, low temperature process and wide selection of masking materials. Yet it also has

disadvantages as to Transient Enhanced Diffusion (TED) and incapability to ultra-shallow doping layer.

Vapor Phase Doping (VPD) solves the problem inherited in ion-implantation. Researchers have shown p+ doping layer of about 30 nm in 1997 [1] and demonstrated an ultra-thin p+ layer of 2nm in 2005 [2]. Using this technology, DUV or EUV photodiode has been demonstrated with ultra-shallow p+/n- junction [3]. It has also been shown that VPD of boron in silicon is TED-free [2]. Besides, VPD of boron could also be used for selective area doping as silicon oxide could be its hard mask. Potentially, it could also be used to passivate and dope sidewall structures.

In the report, I will cover methodology, results and trade-off in development of boron VPD recipe.

### Methodology

Here in SNF, I am using epi2, Reduced Pressure Chemical Vapor Deposition (RPCVD) system from Applied Material. Di-boron gas ( $B_2H_6$ ) diluted in hydrogen ( $H_2$ ) is chosen as doping gas as we could tune its concentration from 100 part per million (ppm) to 0.01ppm. The detailed dilution system will be explained in appendix of supplementary reports.

There are four parameters that may potentially affect doping as listed below in the table.

| Furnace temperature                     | 700°C / 800°C / 900°C |

|-----------------------------------------|-----------------------|

| Furnace pressure                        | 10-200 Torr           |

| B <sub>2</sub> H <sub>6</sub> flow rate | 0.01-100 ppm          |

| B <sub>2</sub> H <sub>6</sub> flow time | 1s – 30min            |

Table 1. Potential parameters to tune in doping and its respect range

Of all these parameters, pressure doesn't play a significant role based on literature review [2,4] so I keep it at 100 Torr. Instead I will focus on furnace temperature,  $B_2H_6$  flow rate and flow time.

To characterize how much doping gets in, C-test wafers were chosen as they are wafers available with lowest phosphor concentration at  $5 \times 10^{14} - 1 \times 10^{15}$  cm<sup>-3</sup>. After doping in epi2, I use four point probes testing to measure sheet resistance of the p+/n- junction formed on wafer surface. As boron doped layers are shallow (~50nm), sheet resistance is expected to be about hundreds to thousands.

The quality of wafer surface after doping is monitored by eye check and by green lamp to see if there is any haziness or particles fall on surface.

### **Results**

## 1. Doping at 700°C

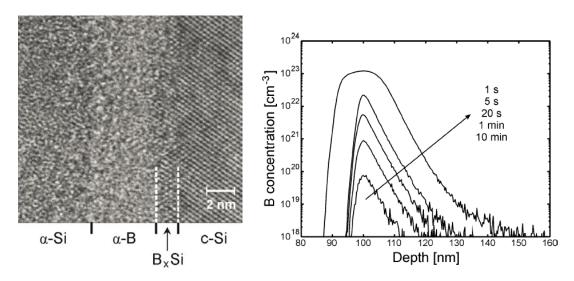

The doping profile at  $700^{\circ}$ C could be explained by the figure below from Ref. [2]. Doping conditions is 6 ppm B<sub>2</sub>H<sub>6</sub> in H<sub>2</sub> environment at atmospheric condition (760 Torr) for different time. TEM show that the interface has a typical stack of 2nm B<sub>x</sub>Si layer plus a slowly growing  $\alpha$ -B layer. B<sub>x</sub>Si itself is highly ohmic but  $\alpha$ -B is semi-metallic with resistivity up to  $10^6$  Ohm\*cm. From SIMS results, the doping increases dramatically with longer doping time while not all boron are electrically activated.

Figure 1. (Left) TEM image of surface doped for 10min, the stack is covered with 100nm PVD  $\alpha$ -Si (right) SIMS measurement of Si stack for 1s to 10min doping. The interface between  $\alpha$ -Si and  $\alpha$ -B is positioned at 100 nm in depth [2]

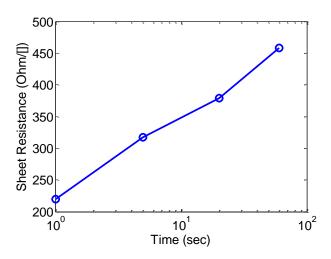

Using a similar condition, I dope N-type wafer with 6 ppm  $B_2H_6$  at  $700^{\circ}C$  and 100 Torr for 1 s, 5 s, 20 s and 1 min. The sheet resistance results below show a monotonic increasing trend for longer doping time, which I would attribute to the slowly growing  $\alpha$ -B layer. This also matches electrical testing results mentioned in the paper as 1s to 5s depostion yields lowest contact resistance [4].

Figure 2. Sheet resistance measurement results of as-deposited wafers

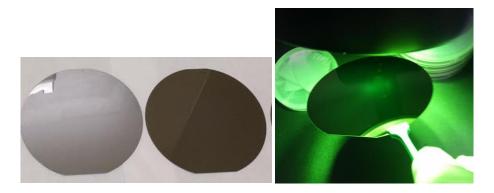

However, this doping methodology has two major problems. The first one is formation of  $\alpha$ -B. As shown below, the color of wafer doped for 10 min turn from clear to bronze. And if checked under the green lamp, haziness suggest less crystalline (or amorphous) surface which could be  $\alpha$ -B.

Figure 3. (Left) Wafers doped for 5min and 10min at 66 ppm B<sub>2</sub>H<sub>6</sub> and 700°C (right) wafer doped at 10min show haziness under green lamp

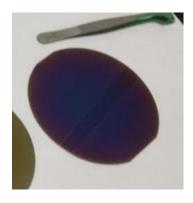

Another problem happens in oxidation of  $B_xSi$  and  $\alpha$ -B. As seen in Fig. 4, after wet oxidation of  $1000^{\circ}C$  for 10 min, the wafer color changed to Purple and Blue compared to uniform dark blue of an ordinary Si wafer. Besides, oxidation thickness is targeted at 100nm, yet actual growth turns out to be 300nm. After dipping in BOE 6:1, this oxide layer turn out to be very diffucult to etch away. This may be due to excess boron that are not electrically activated.

Figure 4. The look of wafer doped for 5min at 66 ppm B<sub>2</sub>H<sub>6</sub> and 700°C after oxidation

### 2. Doping at 900°C

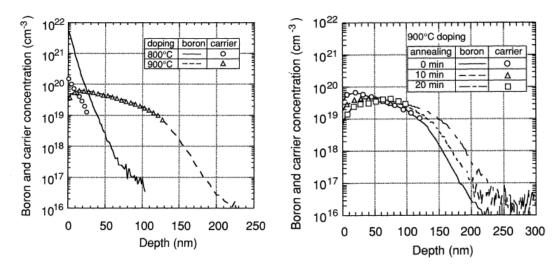

Doping at  $900^{\circ}$ C will solve part of the problem existing in  $700^{\circ}$ C condition. According to Ref [5], doping at  $900^{\circ}$ C could potentially make all boron electrically active. Boron concentration in Fig. 5 is from SIMS measurement while carrier concentration is from differential hall measurement. The doping condition is 2 ppm  $B_2H_6$  at  $900^{\circ}$ C and 760 Torr for 15min. These results show that almost all boron concentration doped at  $900^{\circ}$ C gets electrically activated.

Figure 5. (Left) Boron and carrier concentration profiles just after doping for samples doped at 800°C and 900°C (Right) Boron and carrier concentration profiles for samples doped and annealed at 900°C [5]

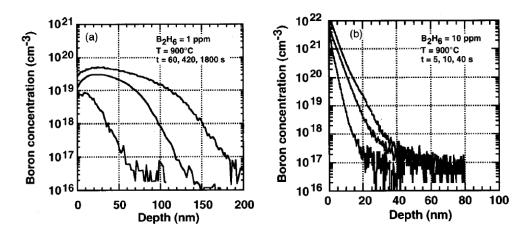

However,  $B_2H_6$  flow rate may also affect how much boron is electrically active. From Ref[6],  $B_2H_6$  flow rate has to be less than 1ppm otherwise boron segregation will happen again on the surface due to higher sticking coefficients.

Figure 6. Boron concentration by SIMS measurement for 1ppm (Left) and 10ppm (Right)  $B_2H_6$  flow rate [6]

As a rough approximation, the peak concentration of 30min 1ppm doping reaches  $5x10^{19}$  cm<sup>-3</sup>, which is almost solid solubility of boron in Si at  $900^{\circ}$ C. Thus an easy model would be comprised of 2 parts, dope and anneal. In the first phase doping, we could assume constant surface concentration diffusion. This will give rise to error function doping profile. In the second phase annealing or oxidation, boron diffuses as in ordinary cases [7].

However, there are two major drawbacks of this model. Firstly, at beginning, surface carrier concentration is proportional to doping time. It is only until the surface carrier concentration reaches solid solubility that it keeps constant. Secondly, boron, whether electrically active or not, will out-diffuse from Si into H<sub>2</sub> environment as well. This could well explain from Figure 6 as there is retrograded region near surface [6].

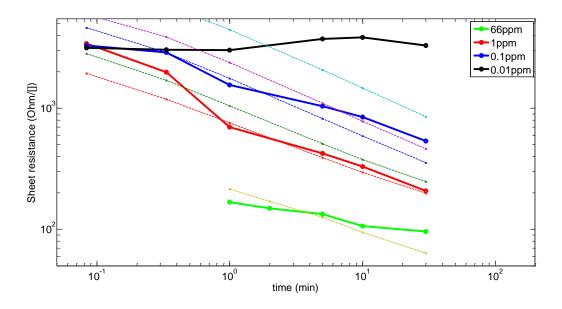

Following on this, I dope on n-type test wafer with different  $B_2H_6$  flow rate (66ppm / 1ppm / 0.1ppm / 0.01ppm) and flow time (5s / 20s / 1min / 5min / 10min / 30min) at  $900^{\circ}$ C. For each recipe, there is 1min post anneal at  $900^{\circ}$ C to avoid boron adsorption when decreasing chamber temperature. The results are shown on figure below.

Figure 7 (Solid lines) sheet resistance of each wafer doped at different flow rate and flow time (dashed lines) expected sheet resistance for each case based on simulation.

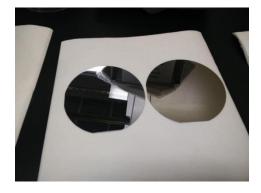

From Fig. 7, the general trend is clear. With longer doping time and larger flow rate, sheet resistance goes down and implies more dopants inside. Samples doped at 0.01ppm may be an outlier since sheet resistance doesn't decrease obviously. This is because the doping recipe is a dynamic balance between adsorption and out-diffusion of boron. It is possible that at this ultra-low concentration of  $B_2H_6$ , boron is easier to out-diffuse. Another outlier is 66ppm doping case, as it is of high concentration and doping profile is exponential. Boron segregates on surface and for longer doping, wafer color also changes to clear bronze. When checking at green lamp, there is no haziness shown, suggesting it is not  $\alpha$ -B any more. Ref[8] reported that  $B_x$ Si layer at 900°C could be as thick as 50nm.

Figure 8. Wafer color contrast between a clear wafer (left) and wafer doped with 66ppm  $B_2H_6$  for 10min (right)

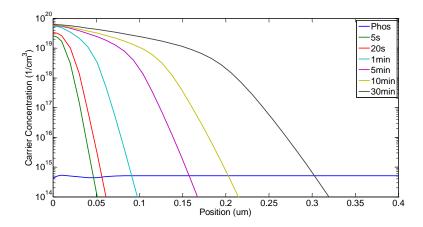

The dashed lines in the figure are results expected by simulation at different constant surface concentrations. From the bottom yellow dashed line at  $6x10^{21}$  cm<sup>-3</sup> up to the top blue dashed line at  $5x10^{19}$  cm<sup>-3</sup>. By comparing simulation to experiments, it's easy to note that for 0.1ppm, its surface concentration keeps decreasing with longer time, this may also be due to low concentration  $B_2H_6$  where out-diffusion dominates. The one that matches really well with the model is 1ppm doping condition, where before 1min, surface concentration gradually increasing and after 1min, it keeps at a constant level at about  $8x10^{19}$  cm<sup>-3</sup>. The simulated doping profile is shown below in Fig. 9.

Figure 9. Simulated doping profile of 1ppm B<sub>2</sub>H<sub>6</sub> doping for different time

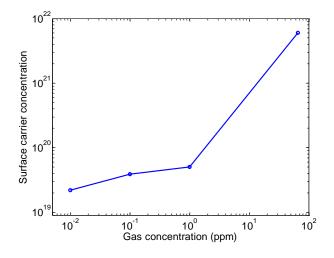

Jumping out, if we compare surface carrier concentration at 1min doping for different flow rate. From 0.01ppm to 1ppm where concentration changes 100 times, surface concentration only see 2.5 times increase. 66ppm does generate a much higher surface concentration at  $6x10^{21}$  cm<sup>-3</sup> but it's due to boron segregation. Therefore, if we work in a region where all boron gets electrically activated, dopant flow rate will not play a significant role in doping profile compared to doping time.

Figure 10. Comparison of surface carrier concentration at 1min doping of different doping flow rate

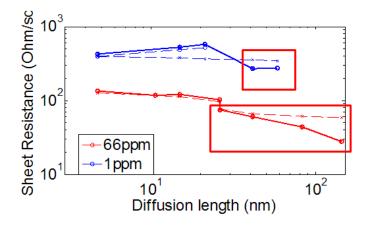

Getting an initial doping profile is important. But if we would like to tune doping profile, we need to do thermal anneal or oxidation. Here I picked two groups of wafers, one is 1ppm doping for 5min and the other is 66ppm doping for 5min. I then put these wafers in H<sub>2</sub> environment (epi2) to anneal.

Figure 11. Sheet resistance of wafers after annealing in H<sub>2</sub> environment. Solid lines are experiment results, while dashed lines are simulation results

Annealing is done in different temperature (900°C / 100°C) and different time (1min – 20min). Characteristic diffusion length is put as figure of merits for different annealing conditions. Data points outside red box is annealed at 900°C while inside is 1000°C. For 900°C, there is increase in sheet resistance which is mainly due to boron out-diffusion [5]. After considering this issue, the blue dashed line with circle match pretty well with experiment results. 66ppm case also matches very well without out-diffusion fitting. My guess is that excess boron that is not electrically active become activated and thus compensates out-diffusion. However, both doping cases differ from simulation in 1000°C. I suppose this is either due to higher solid solubility at 1000°C or due to less out-diffusion at 1000°C.

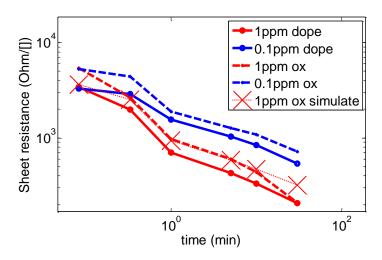

Oxidation is also performed for two groups of wafers. One group is 1ppm doping for different doping time, and the other is 0.1ppm doping for different doping time. Oxidation recipe is fixed at wet oxidation at  $1000^{\circ}$ C and targeted at 100nm thermal oxide.

Figure 12. Sheet resistance of wafers before and after oxidation, dashed lines with red cross is expected results from simulation

From the results, we could note an increase in sheet resistance as boron tends to go into oxide during oxidation. At the same time, simulation show a good match with experiments for wafers doped with 1ppm  $B_2H_6$  at different time.

#### Conclusion

After this work, we have two recipes that will work for doping boron directly in Si. The first recipe is to dope at 6ppm for 1s-5s at  $700^{\circ}$ C. This will form a 2nm thick highly ohmic B<sub>x</sub>Si. But thermal oxidation is not recommended as oxide will be difficult to etch away. The second recipe is to dope at 1ppm for 1min – 30min at  $900^{\circ}$ C. The incorporated boron will all be electrically activated and thermal oxidation or annealing both works.

Besides, a simulation code using Sprocess from Sentaurus is developed to see expected doping profile. It will be covered in the supplementary reports.

#### **Future work**

There are two parts, which I would like to cover in the future community service.

- 1) Baking tests to strip native oxide on Si surface. I would like to lower the temperature and time compared to my current recipe 1150°C for 10min.

- 2) Demonstrate that doping also works on sidewall. This will need IV measurement.

# Acknowledgement

I would like to thank Maurice Stevens for answering all my questions about furnace and working with Ted Berg and Sean in bring up the epi chamber and checking gas line. I would also want to thank Prof. Ted Kamins and Prof. James Harris for the helpful discussion and insightful guidance in my work.

### Reference

- [1] Kiyota, Yukihiro, et al. "Role of hydrogen during rapid vapor-phase doping analyzed by x-ray photoelectron spectroscopy and Fourier-transform infrared-attenuated total reflection." Journal of Vacuum Science & Technology A 16.1 (1998): 1-5.

- [2] Sarubbi, Francesco, Lis K. Nanver, and Tom L. Scholtes. "CVD delta-doped boron surface layers for ultra-shallow junction formation." ECS Transactions 3.2 (2006): 35-44.

- [3] Sarubbi, F.; Nanver, L.K.; Scholtes, T.L.M.; Nihtianov, S.N., "Extremely Ultra -Shallow p+-n Boron-Deposited Silicon Diodes Applied to DUV Photodiodes," Device Research Conference, 2008, vol., no., pp.143,144, 23-25 June 2008

- [4] Sarubbi, Francesco, Tom LM Scholtes, and Lis K. Nanver. "Chemical vapor deposition of  $\alpha$ -boron layers on silicon for controlled nanometer-deep p+ n junction formation." Journal of electronic materials 39.2 (2010): 162-173.

- [5] Kiyota, Yukihiro, et al. "Behavior of active and inactive boron in Si produced by vapor-phase doping during subsequent hydrogen annealing." Japanese journal of applied physics 34.6R (1995): 2981.

- [6] Kiyota, Yukihiro, and Taroh Inada. "Sticking coefficient of boron and phosphorus on silicon during vapor-phase doping." Journal of Vacuum Science & Technology A 19.5 (2001): 2441-2445.

- [7] Kiyota, Yukihiro, et al. "Characteristics of Shallow Boron Doped Layers in Si by Rapid Vapor Phase Direct Doping." Journal of The Electrochemical Society 140.4 (1993): 1117-1121.

- [8] Tseng, H C., F. M. Pan, and C. Y. Chang. "Characterization of boron silicide layer deposited by ultrahigh vacuum chemical vapor deposition." Journal of applied physics 80.9 (1996): 5377-5383.