# Low-T, High- $\kappa$ Dielectrics for Transparent/ Flexible 2D Electronics

Kirby Smithe

EE 412 – Advanced Nanofabrication Laboratory

25 slides

# Outline

- Introduction and Motivation

- Methodology

- Benchmark ALD Oxides

- Processing on PDMS

- Processing on PEN

- Conclusions and Future Work

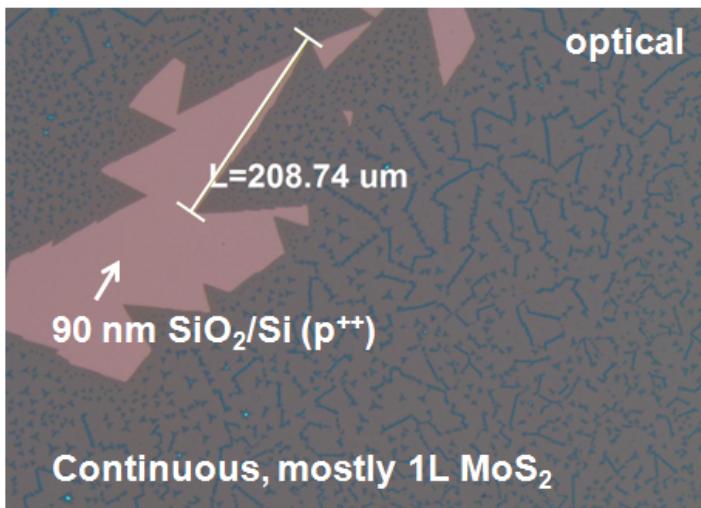

1L G/1L MoS<sub>2</sub>/PDMS/Batman

# Motivation – Transparent/Flexible 2D Oxides

- **NEED: Low-T, high- $\kappa$ , flexible-compatible, thin film oxides**

# Motivation – Transparent/Flexible 2D Oxides

- Y. Wu, S. Yu, and S. Li with J. Provine (EE 412, Fall 2010)

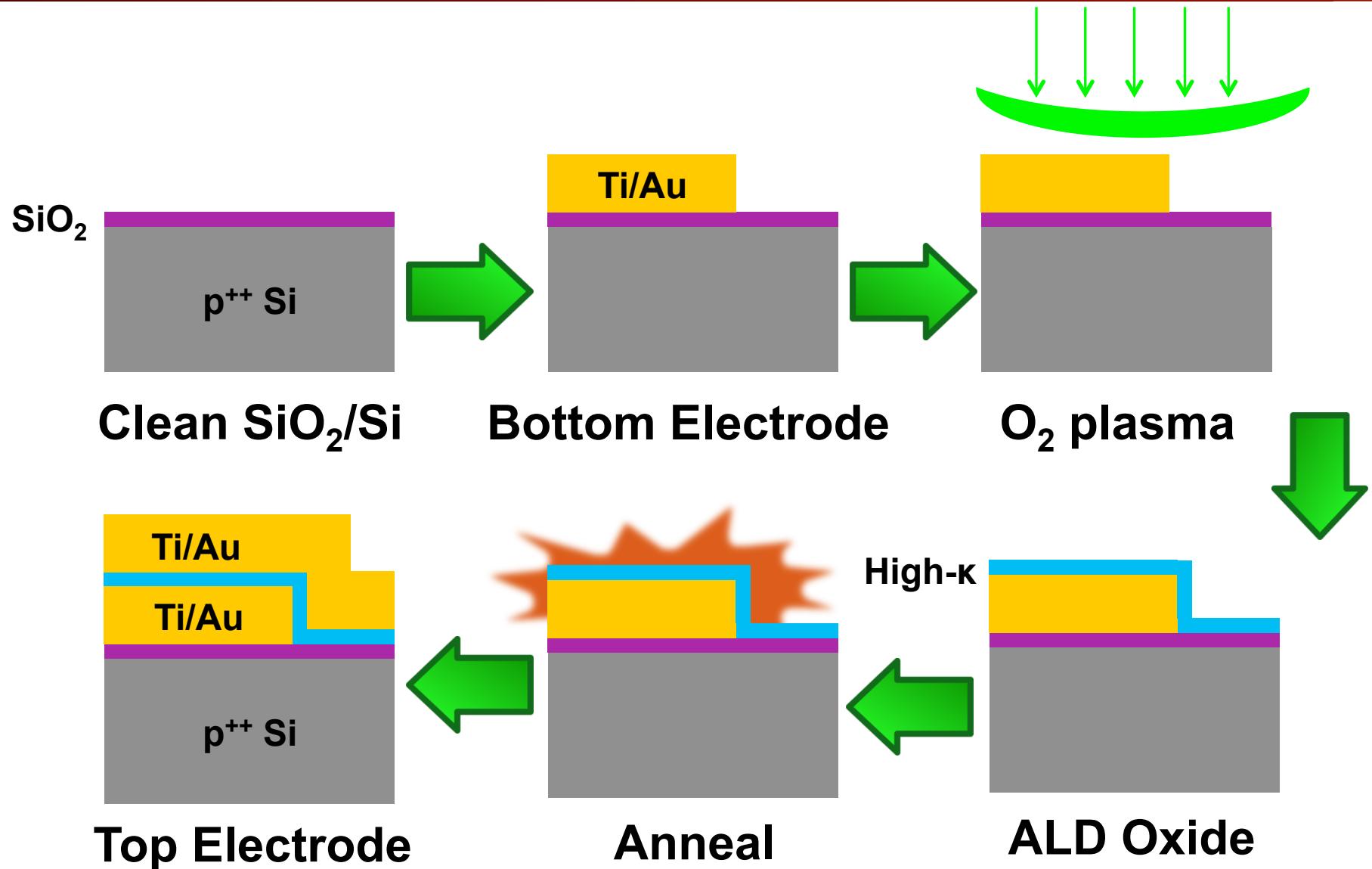

# Methodology – Process Flow

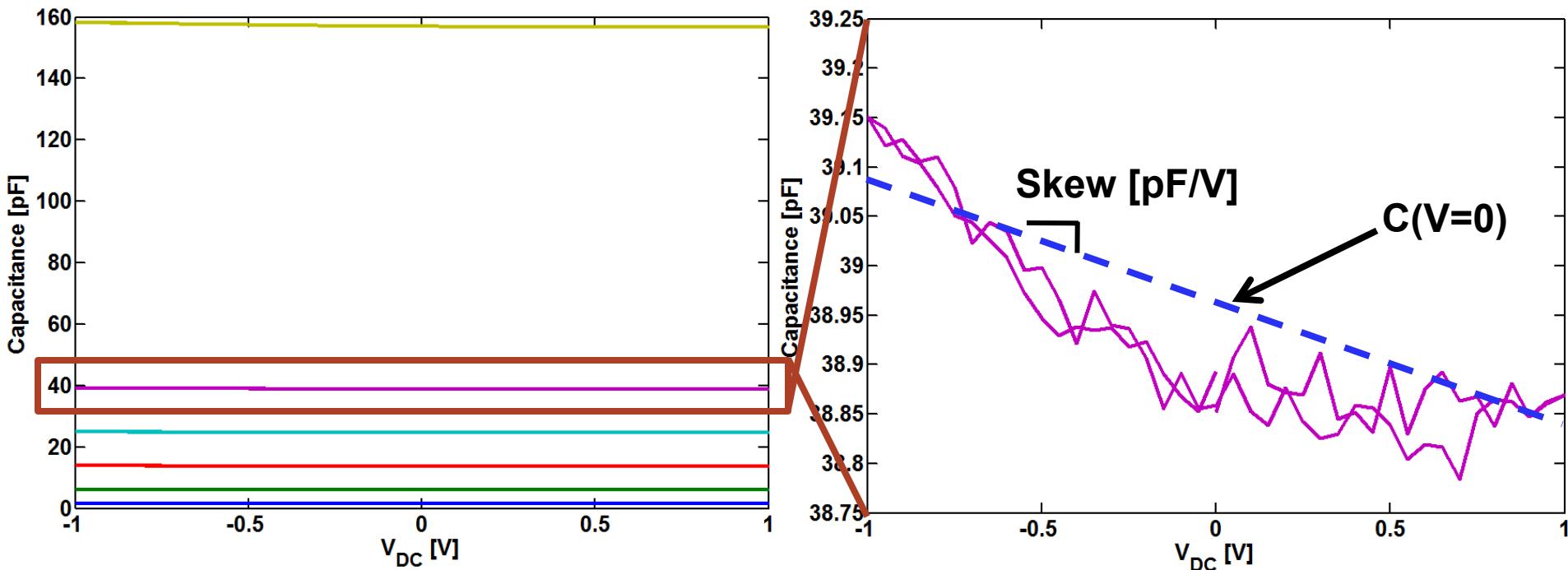

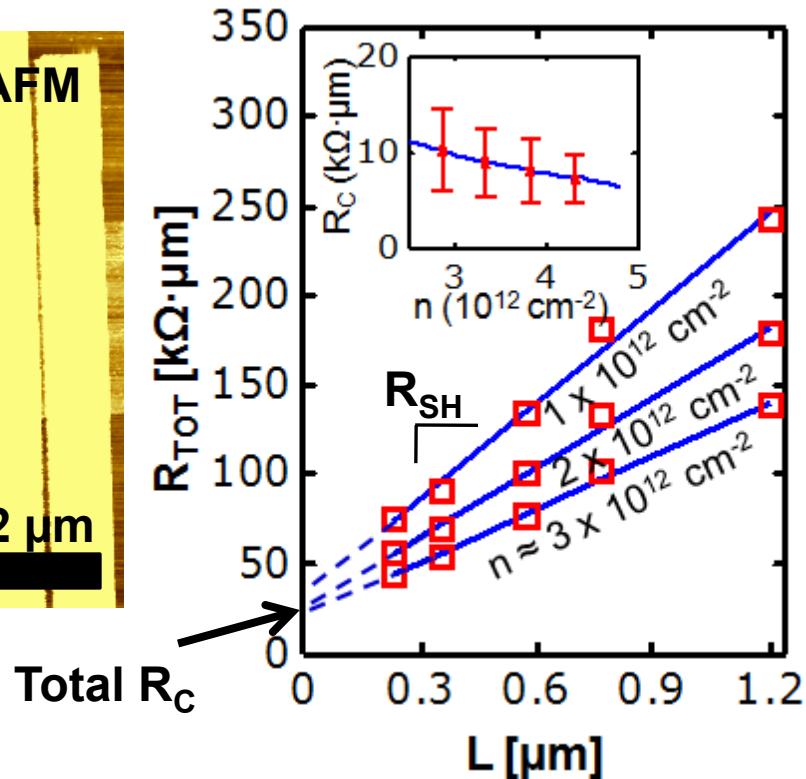

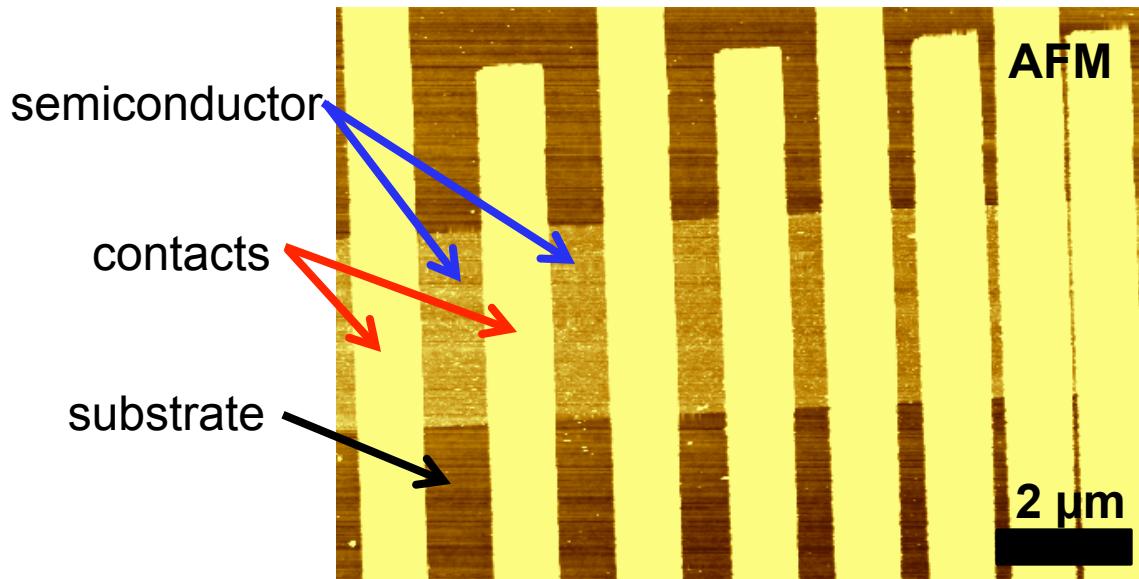

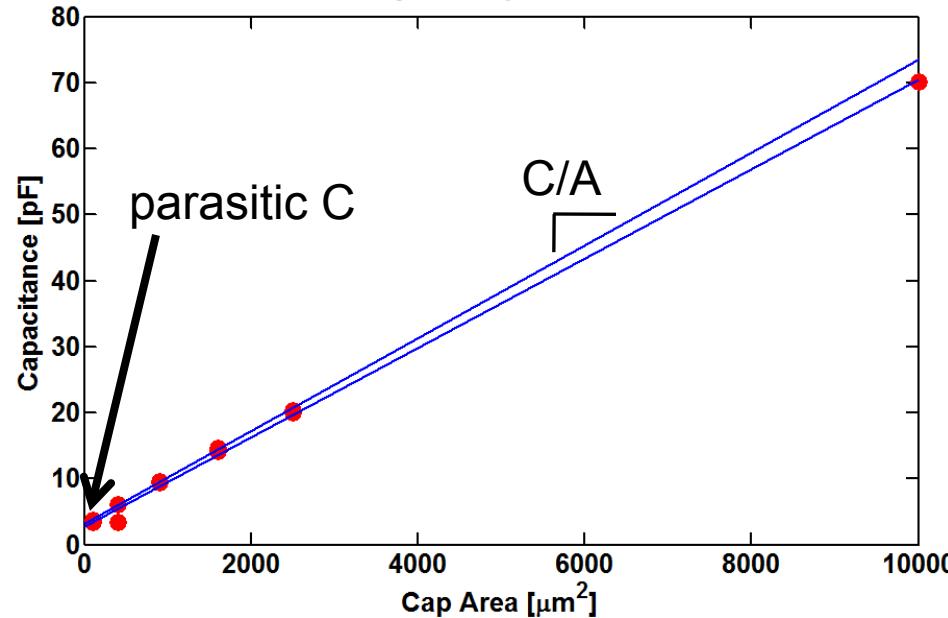

# Methodology – Measurements

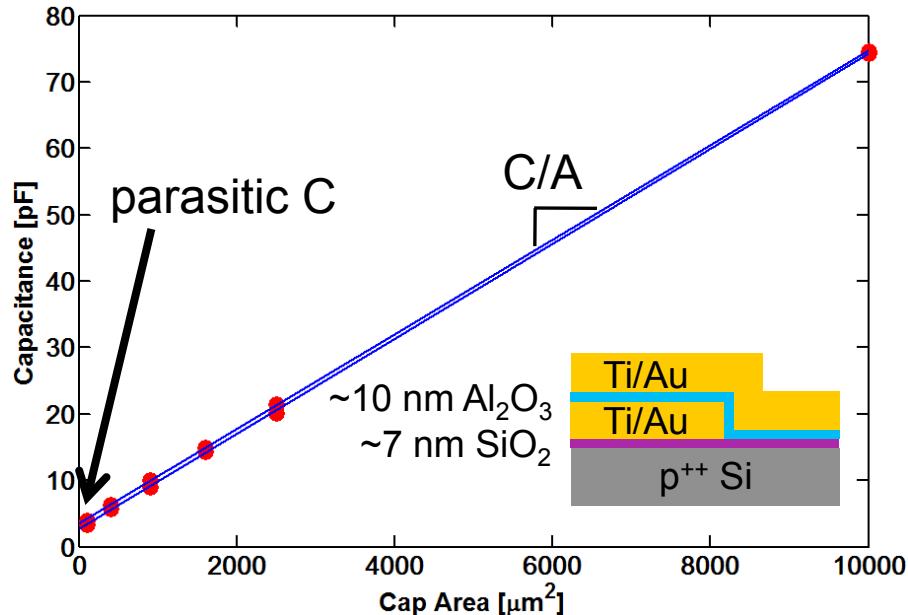

- All caps were measured from  $0 \rightarrow 1 \rightarrow -1 \rightarrow 0$  V.

- Capacitances changed by <1% over this range.

- A line was fit to the data, with the slope being the “skew” and the C-V intercept value taken for fitting C/A.

# Methodology – Capacitor “TLM” Arrays

We can do the same thing with capacitors!

# Outline

- Introduction and Motivation

- Methodology

- Benchmark ALD Oxides

- Processing on PDMS

- Processing on PEN

- Conclusions and Future Work

1L G/1L MoS<sub>2</sub>/PDMS/Batman

# Savannah - 150 °C Alumina + 200 °C FGA

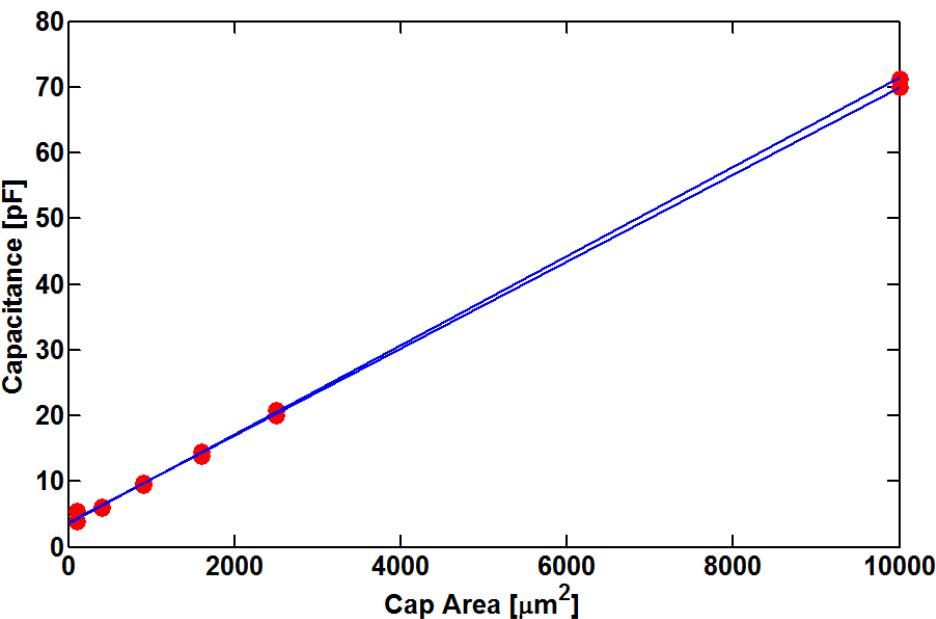

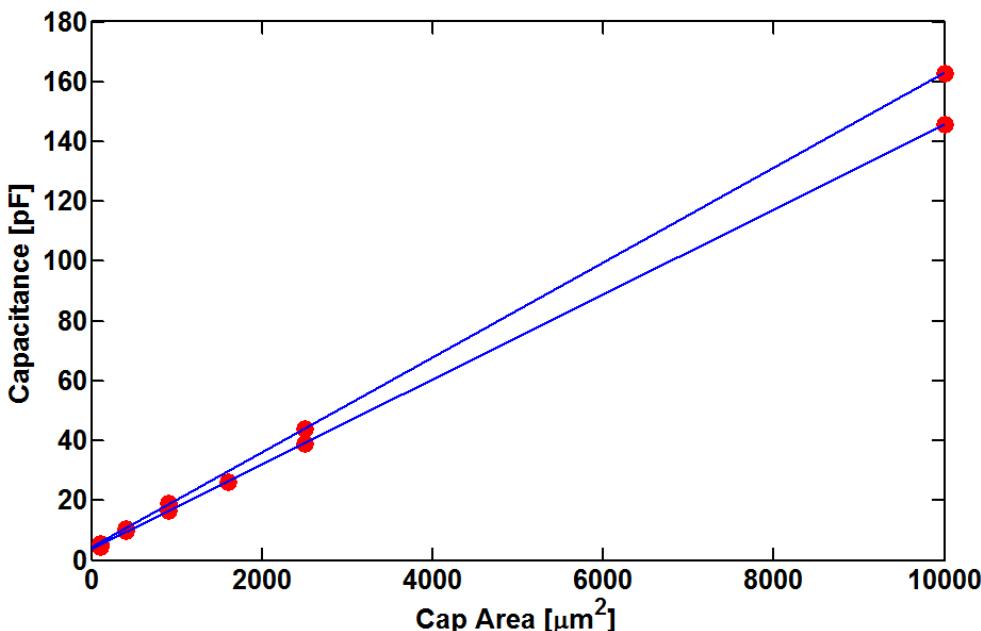

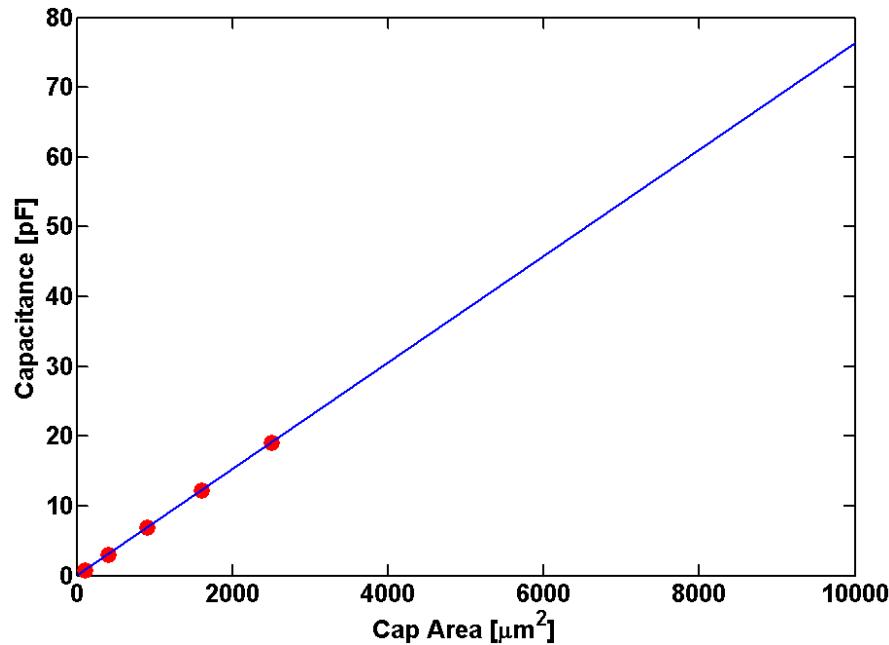

## C vs. A

- $C = 0.716 \pm 0.009$

- $0.713 \pm 0.006 \mu\text{F}/\text{cm}^2$

- $R^2 = 1.000, 1.000$

- $d = 9.4 \text{ nm}$

- $\kappa = 7.60 \pm 0.10, 7.56 \pm 0.06$

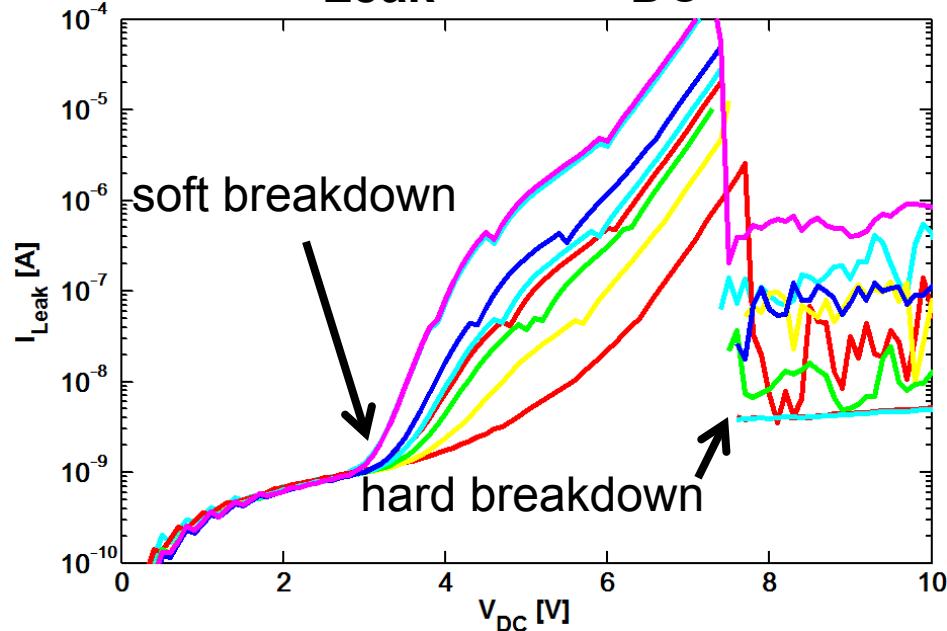

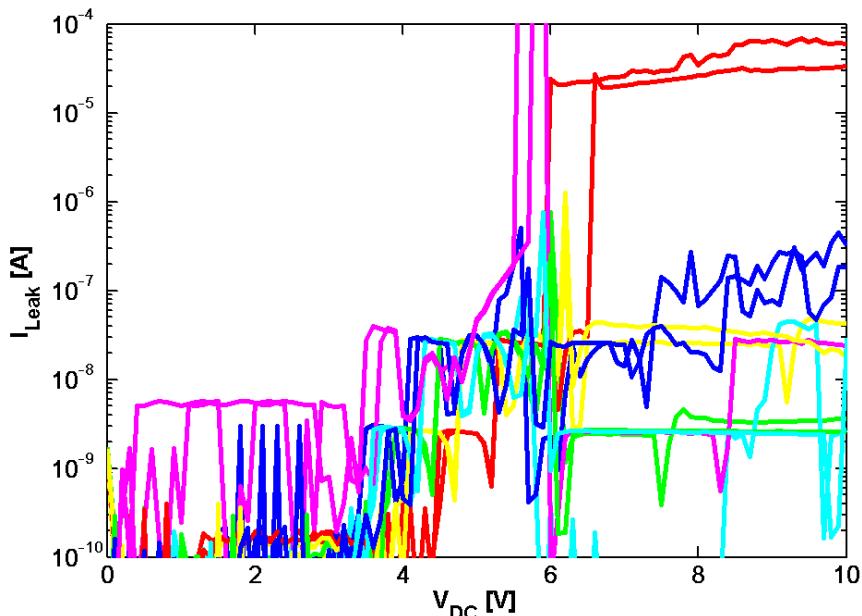

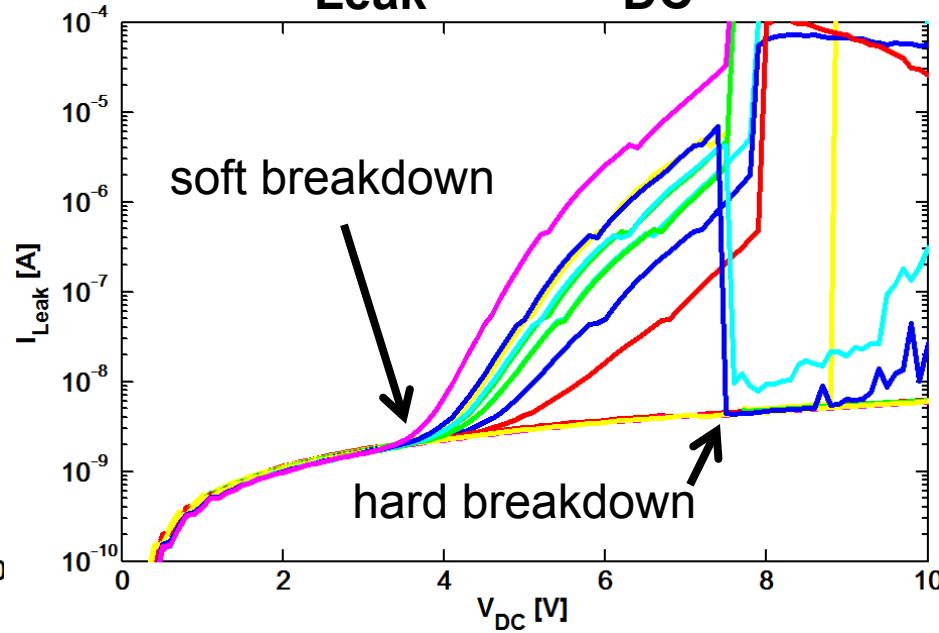

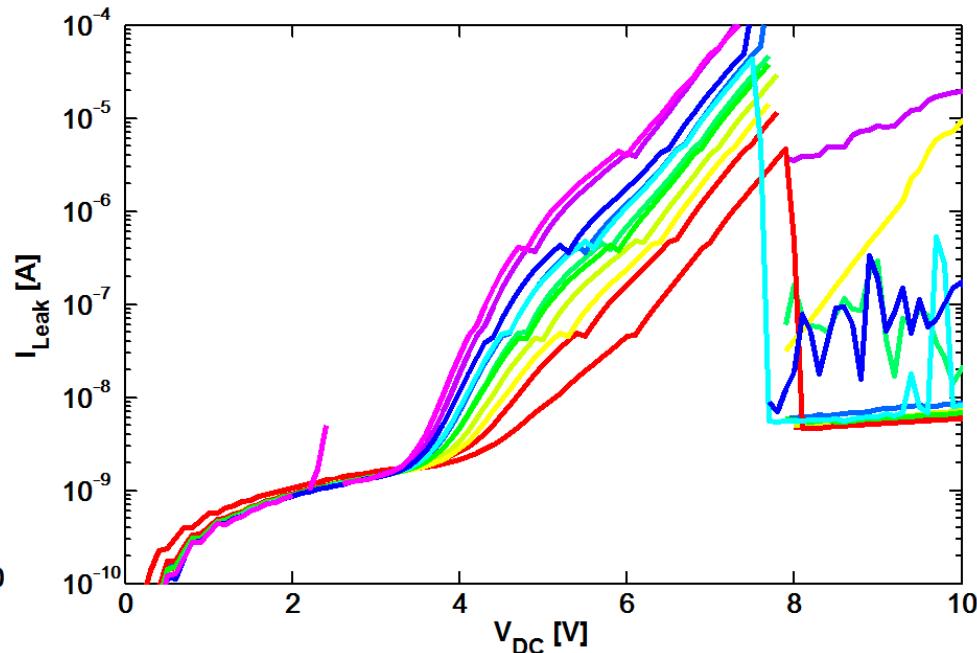

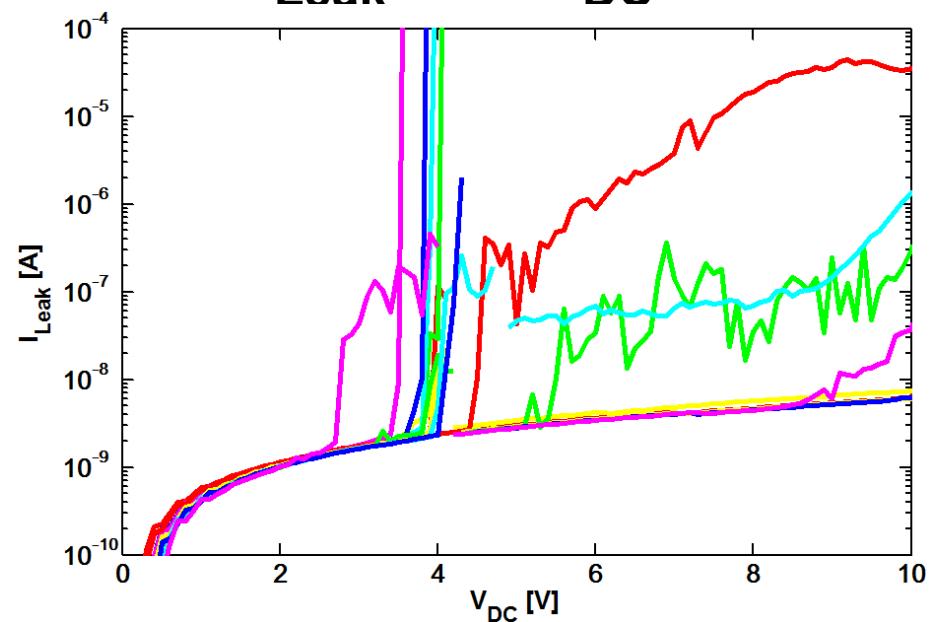

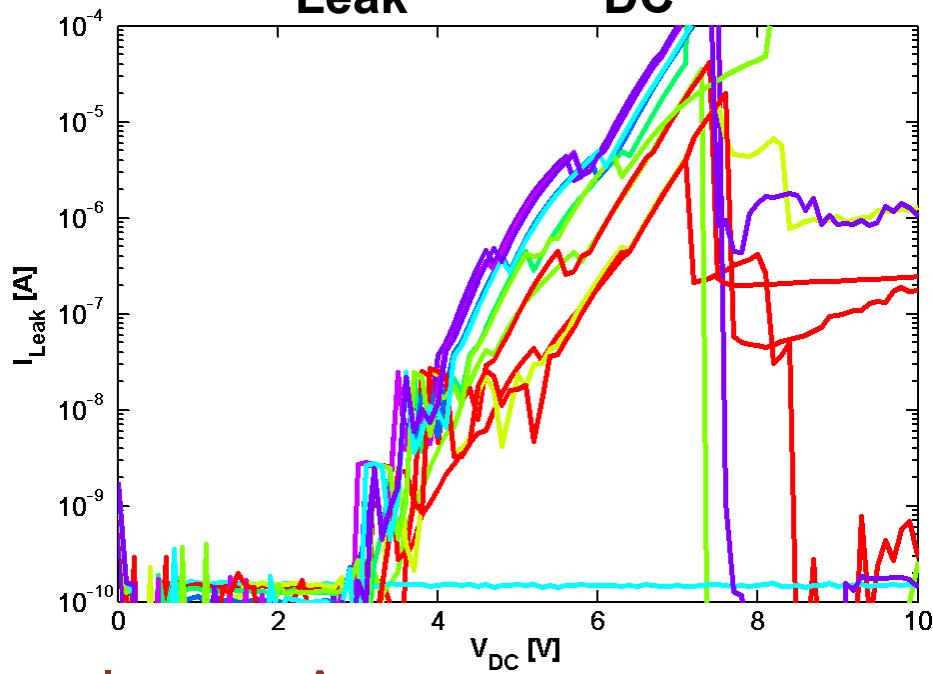

## I<sub>Leak</sub> vs. V<sub>DC</sub>

- $I_{\text{Leak}} < n\text{A}$

- $V_{\text{BD,soft}} \sim 3.0 \text{ V}$

- $E_{\text{crit,soft}} \sim 0.32 \text{ V/nm}$

- $V_{\text{BD,hard}} > 7.0 \text{ V}$

- $E_{\text{crit,hard}} \sim 0.74 \text{ V/nm}$

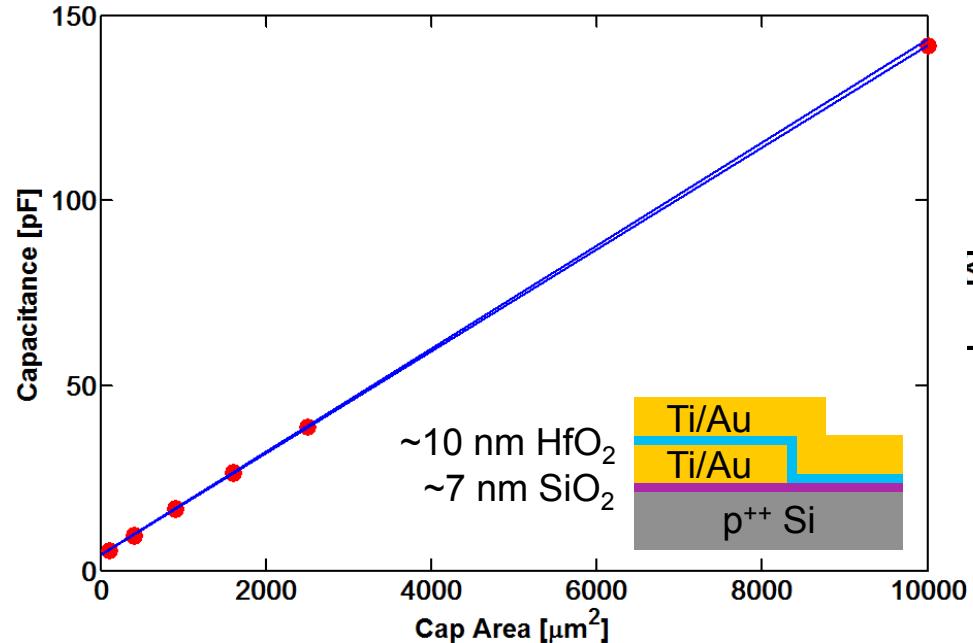

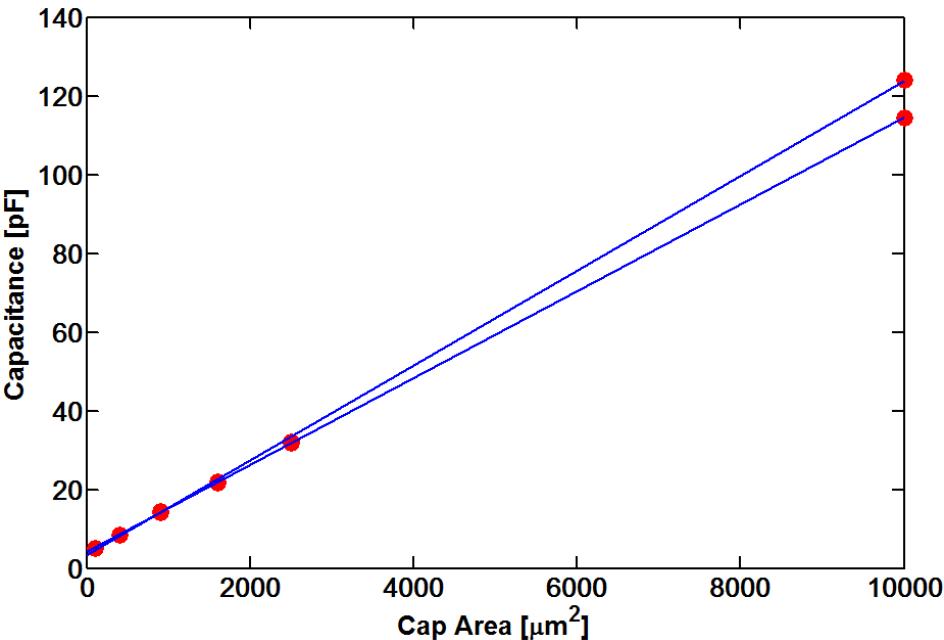

# Savannah - 150 °C Hafnia + 200 °C FGA

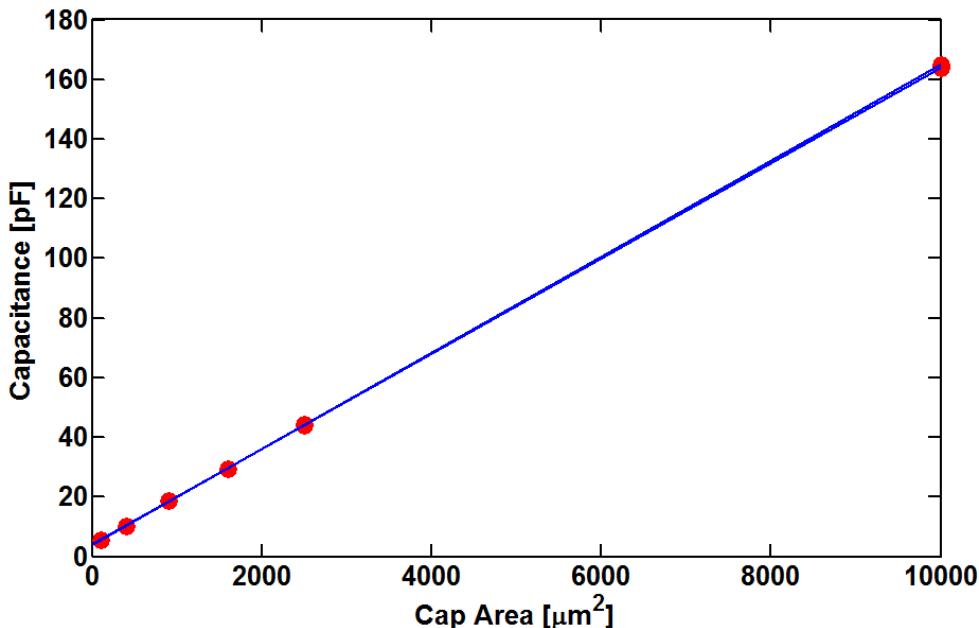

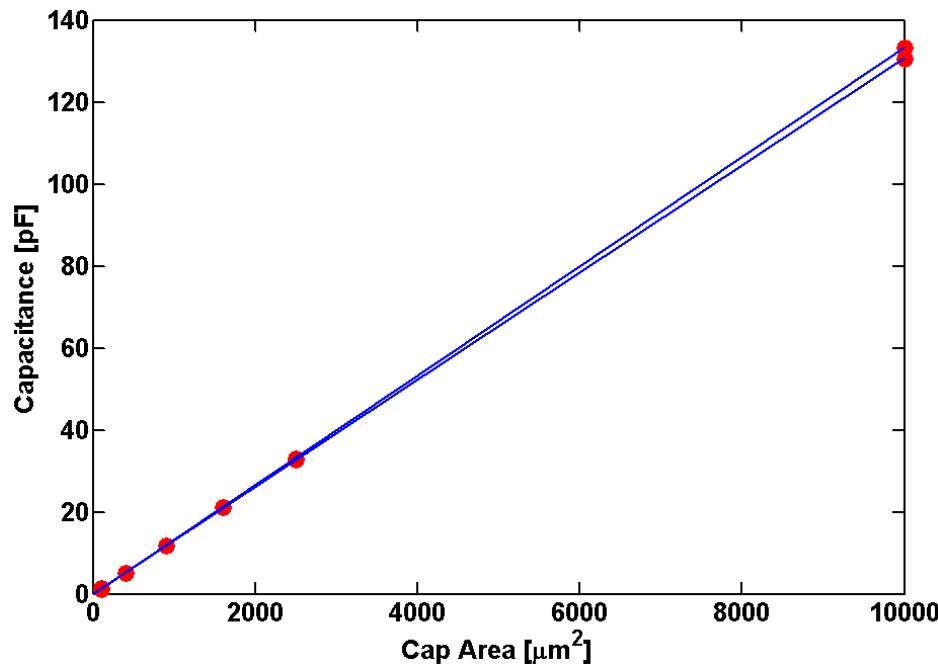

**C vs. A**

- $C = 1.39 \pm 0.02$

- $1.38 \pm 0.01 \text{ } \mu\text{F}/\text{cm}^2$

- $R^2 = 1.000, 1.000$

- $d = 10.5 \text{ nm}$

- $\kappa = 16.5 \pm 0.3, 16.3 \pm 0.1$

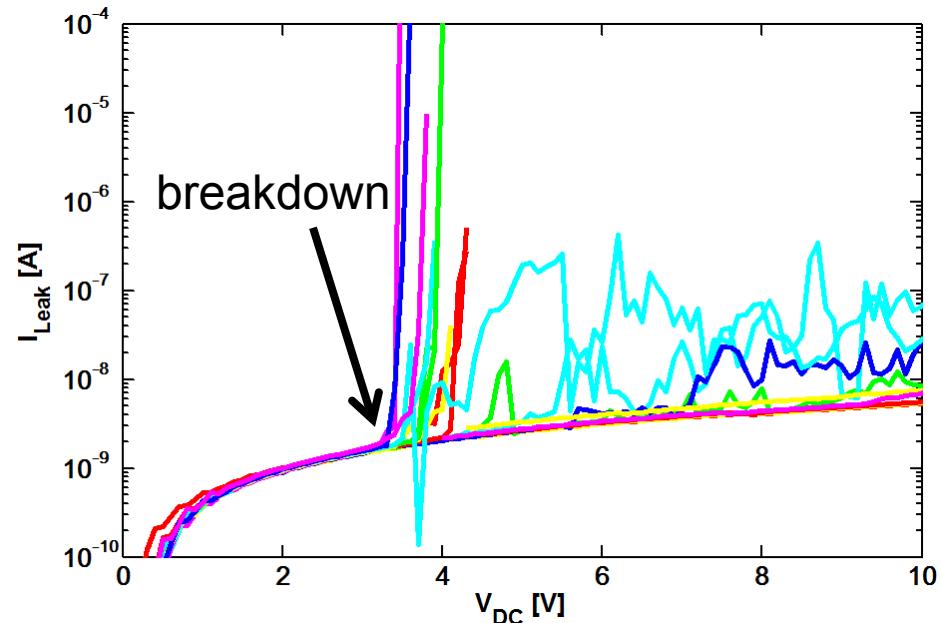

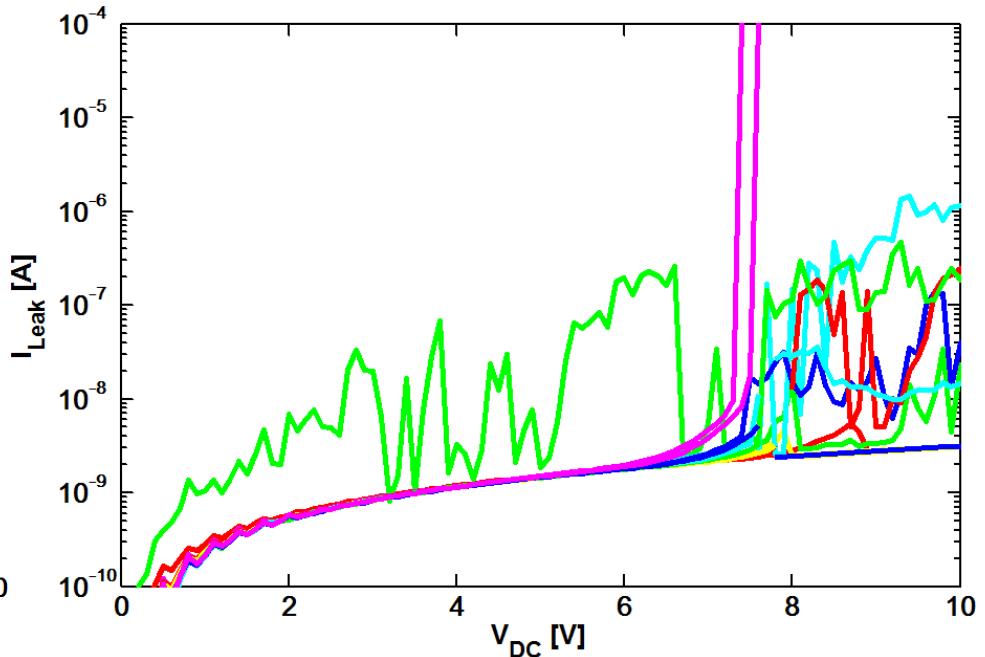

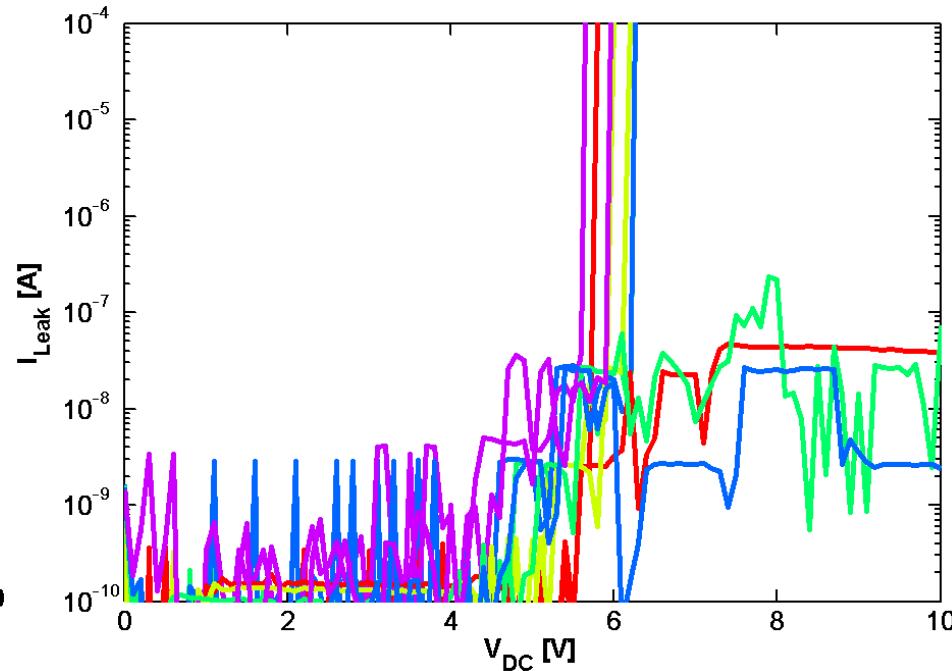

**$I_{\text{Leak}}$  vs.  $V_{\text{DC}}$**

- $I_{\text{Leak}} < \text{nA}$

- $V_{\text{BD}} > 4.5 \text{ V}$

- $E_{\text{crit}} \sim 0.43 \text{ V/nm}$

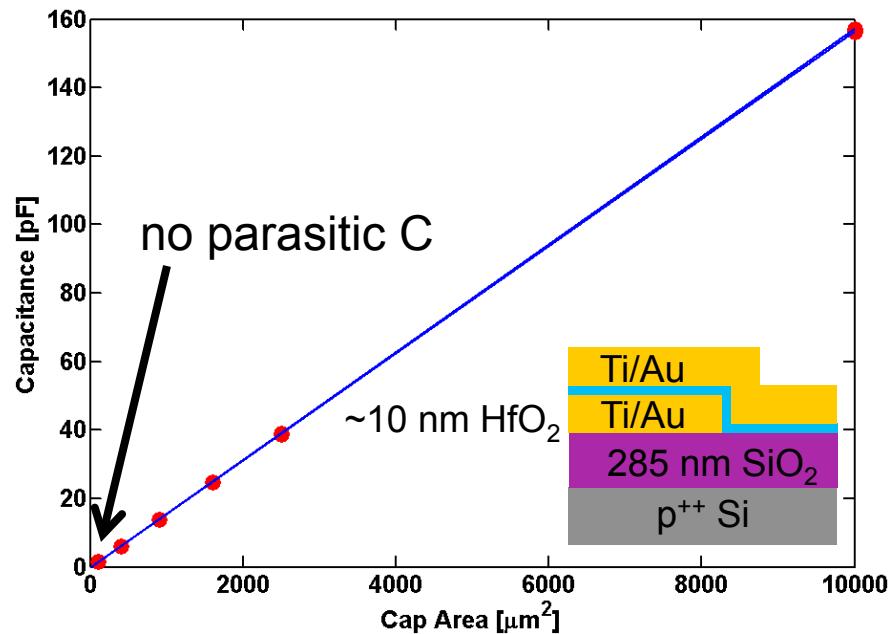

# MVD - 125 °C Hafnia + 125 °C FGA

**C vs. A**

- $C = 1.57(4) \pm 0.004$

- $1.56(6) \pm 0.004 \mu\text{F}/\text{cm}^2$

- $R^2 = 1.000, 1.000$

- $d \approx 11.2 \text{ nm}$

- $\kappa \approx 15.9 \pm 0.1, 15.8 \pm 0.1$

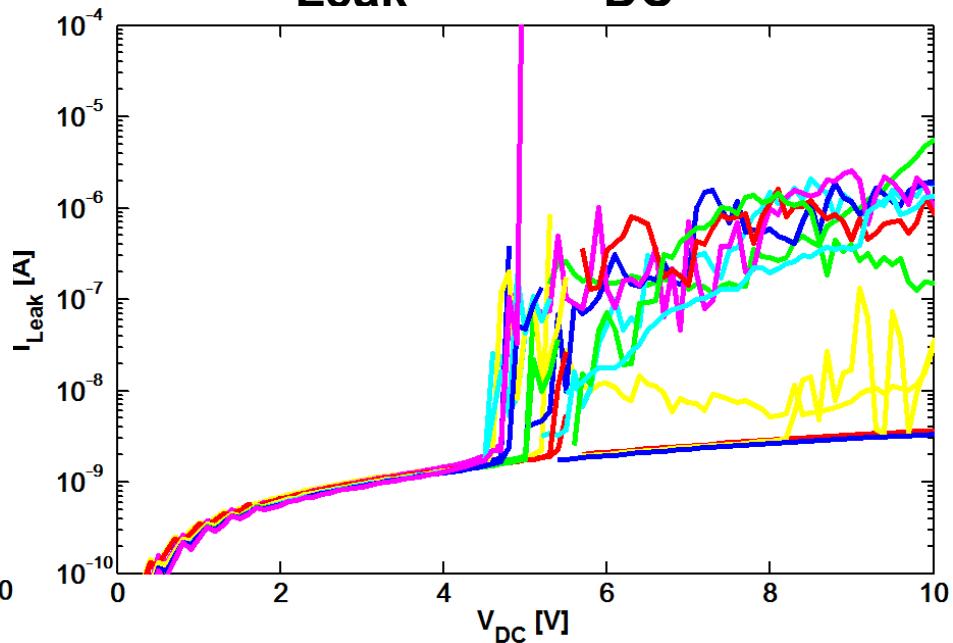

**$I_{\text{Leak}}$  vs.  $V_{\text{DC}}$**

- $I_{\text{Leak}} < \text{nA}$

- $V_{\text{BD}} > 5.5 \text{ V}$

- $E_{\text{crit}} \sim 0.49 \text{ V/nm}$

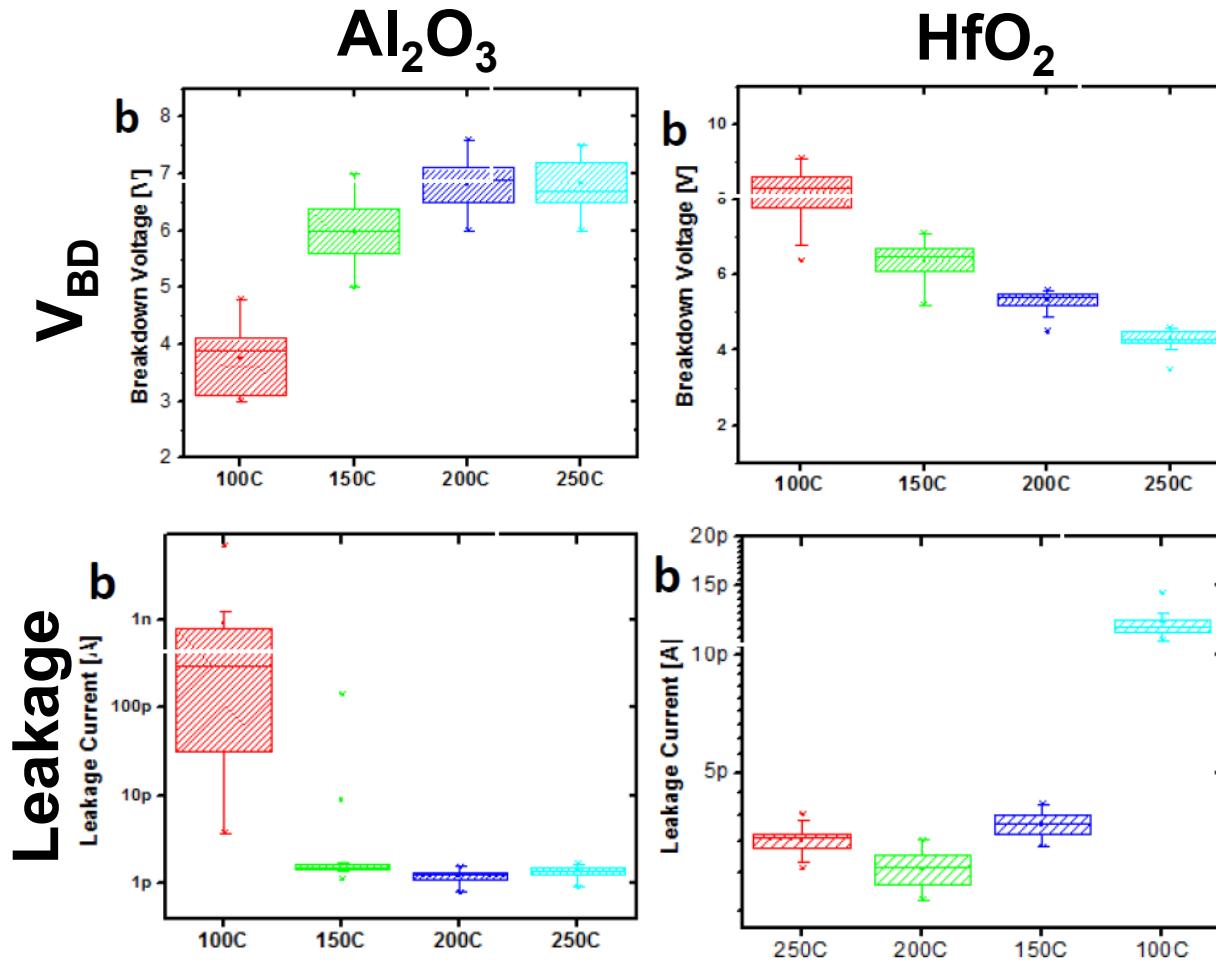

# Results – Benchmark ALD Oxides on SiO<sub>2</sub>

| Savannah                 | Alumina                |             |        |        | Hafnia                 |             |        |        |

|--------------------------|------------------------|-------------|--------|--------|------------------------|-------------|--------|--------|

|                          | 200 °C                 | 200 °C      | 150 °C | 100 °C | 200 °C                 | 200 °C      | 150 °C | 100 °C |

| anneal                   | + 50 °C O <sub>2</sub> | + 50 °C FGA |        |        | + 50 °C O <sub>2</sub> | + 50 °C FGA |        |        |

| d [nm]                   | 10.0                   | 10.0        | 9.4    | 8.4    | 8.7                    | 8.7         | 10.5   | 11.9   |

| Skew [pF/V]              | ~0.15                  | ~0.01       | ~0.15  | X      | ~0.2                   | ~0.2        | ~0.1   | ~0.15  |

| C [μF/cm <sup>2</sup> ]  | 0.670                  | 0.690       | 0.715  | X      | 1.51                   | 1.61        | 1.39   | 1.15   |

| κ                        | 7.6                    | 7.8         | 7.6    | X      | 14.8                   | 15.8        | 16.4   | 15.5   |

| I <sub>Leak</sub>        | <nA                    | <nA         | <nA    | X      | <nA                    | <nA         | <nA    | <nA    |

| V <sub>BD</sub> [V]      | >3.5                   | >3.5        | >3.0   | X      | >3.2                   | >3.2        | >4.5   | >6.0   |

| E <sub>crit</sub> [V/nm] | 0.35                   | 0.35        | 0.32   | X      | 0.37                   | 0.37        | 0.43   | 0.50   |

| MVD                      | Alumina |        | Hafnia |        |

|--------------------------|---------|--------|--------|--------|

|                          | 125 °C  | 100 °C | 125 °C | 100 °C |

| ALD temp                 | 125 °C  | 100 °C | 125 °C | 100 °C |

| FGA                      | 125 °C  | 100 °C | 125 °C | 100 °C |

| d [nm]                   | ~8.9*   | 6.9    | ~11.2* | 11.3   |

| Skew [pF/V]              | ~0.05   | X      | ~0.7   | ~0.4   |

| C [μF/cm <sup>2</sup> ]  | 0.760   | X      | 1.57   | 1.32   |

| κ                        | ~7.7*   | X      | ~16*   | 13.2   |

| I <sub>Leak</sub>        | <nA     | X      | <nA    | <nA    |

| V <sub>BD</sub> [V]      | >3.0    | X      | >5.5   | >5.5   |

| E <sub>crit</sub> [V/nm] | ~0.34   | X      | ~0.49  | 0.49   |

\*d interpolated from Savannah data

- Savannah and MVD oxides are quite similar.

- Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> show opposite trends in thickness, capacitance, and breakdown at lower temperatures.

- HfO<sub>2</sub> seems to be a considerably more stable process at low T.

# Outline

- Introduction and Motivation

- Methodology

- Benchmark ALD Oxides

- Processing on PDMS

- Processing on PEN

- Conclusions and Future Work

1L G/1L MoS<sub>2</sub>/PDMS/Batman

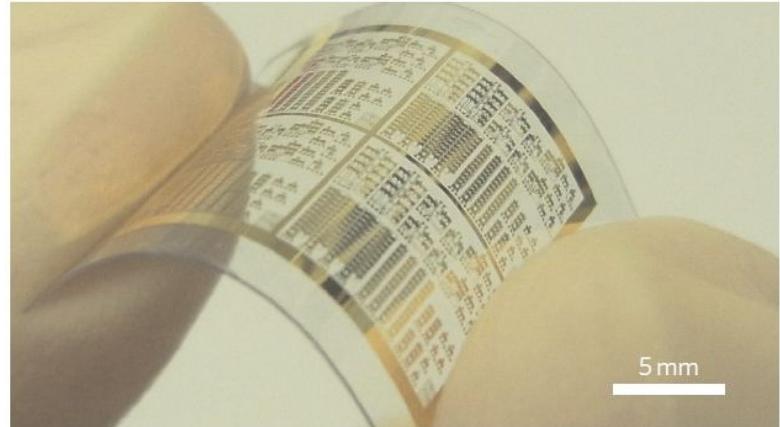

# Overview – Processing on Flexibles

|                      | Hotplate<br>Curing | Ovens<br>$\geq 150\text{ }^{\circ}\text{C}$ | Direct<br>SPR 3612 | Oxide/Metal<br>Cracking | Thermal<br>Wrinkling | Trivial<br>Alignment |

|----------------------|--------------------|---------------------------------------------|--------------------|-------------------------|----------------------|----------------------|

| SiO <sub>2</sub> /Si | yes ✓              | yes ✓                                       | yes ✓              | no ✓                    | no ✓                 | yes ✓                |

| PDMS                 | no ✗               | no ✗                                        | no ✗               | yes ✗                   | yes ✗                | yes ✓                |

| PEN                  | yes ✓              | no ✗                                        | ? ?                | no ✓                    | no ✓                 | no ✗                 |

- Spoiler: PEN is easier to work with as a substrate than PDMS

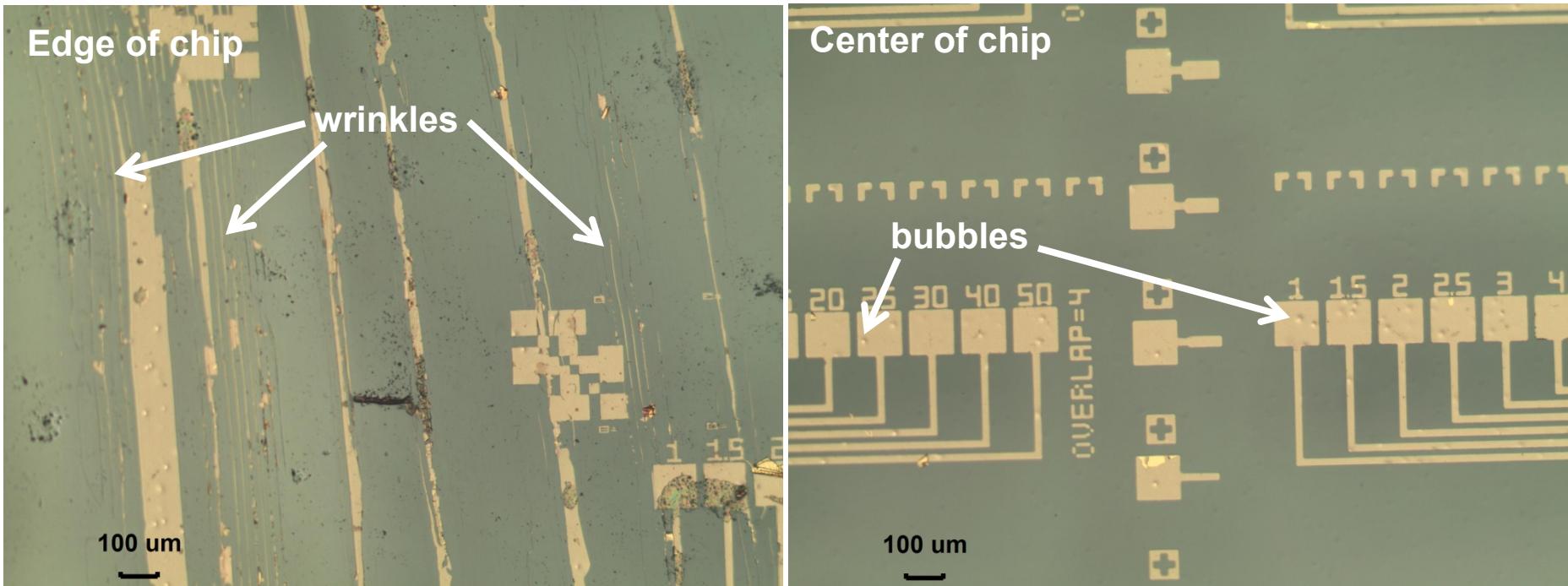

# Initial Cap Pads on PDMS

- PDMS thoroughly outgassed for 2 hours in vacuum and baked at 80 °C for 2 hours in ambient oven.

- PMGI (liftoff layer) baked on at 200 °C for 5 minutes

- Strong temperature gradient caused visible wrinkles near edges

- SPR 3612 baked in 90 °C oven for 25 minutes

- ~1 cm<sup>2</sup> in center of 2×2 cm chip had bubbles but no wrinkles

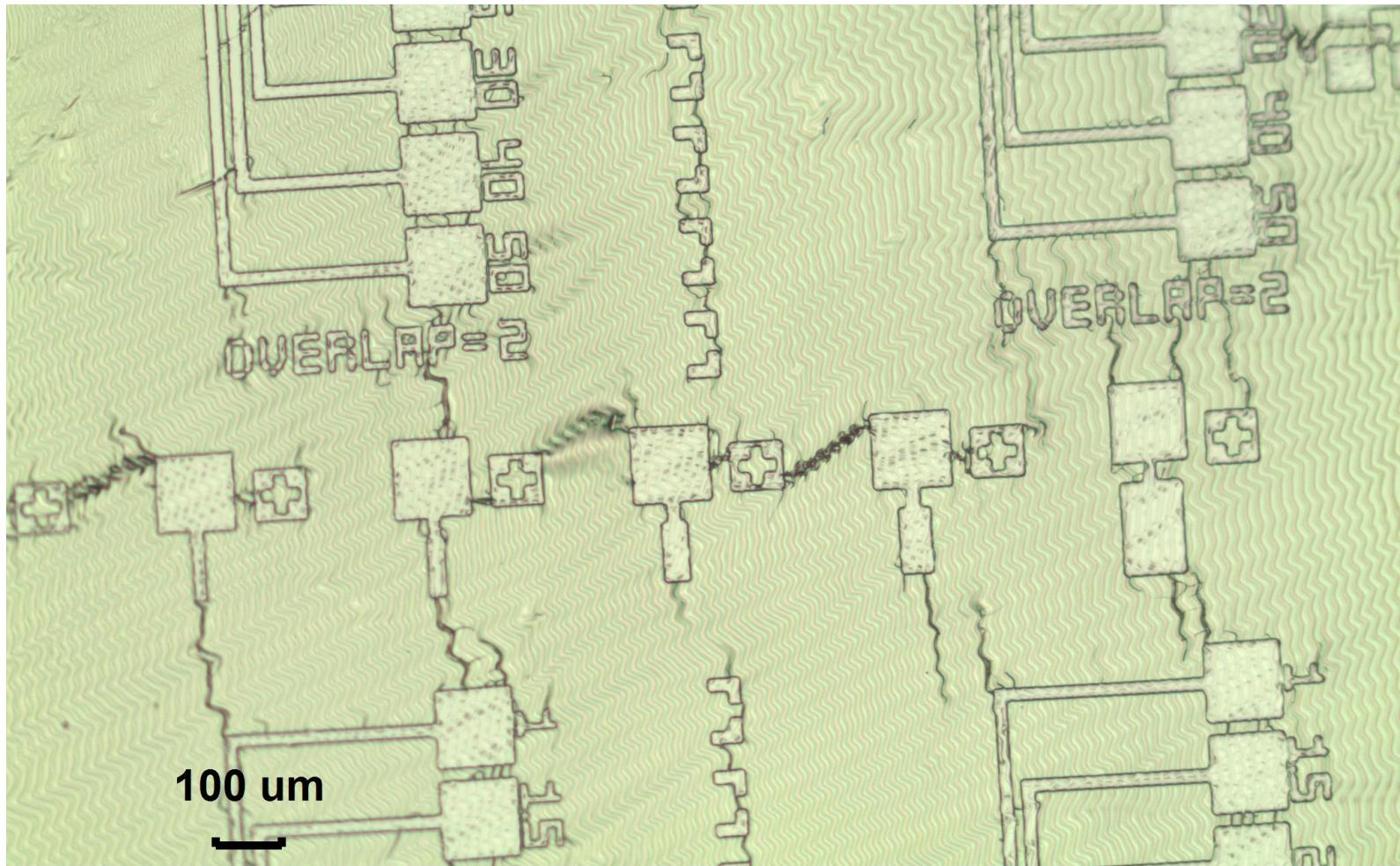

# Cap Pads on PDMS – 2<sup>nd</sup> Try

- PMGI spun on at 3000 rpm

- 230 °C bake in white oven for 25 mins (+ SPR 3612 and develop)

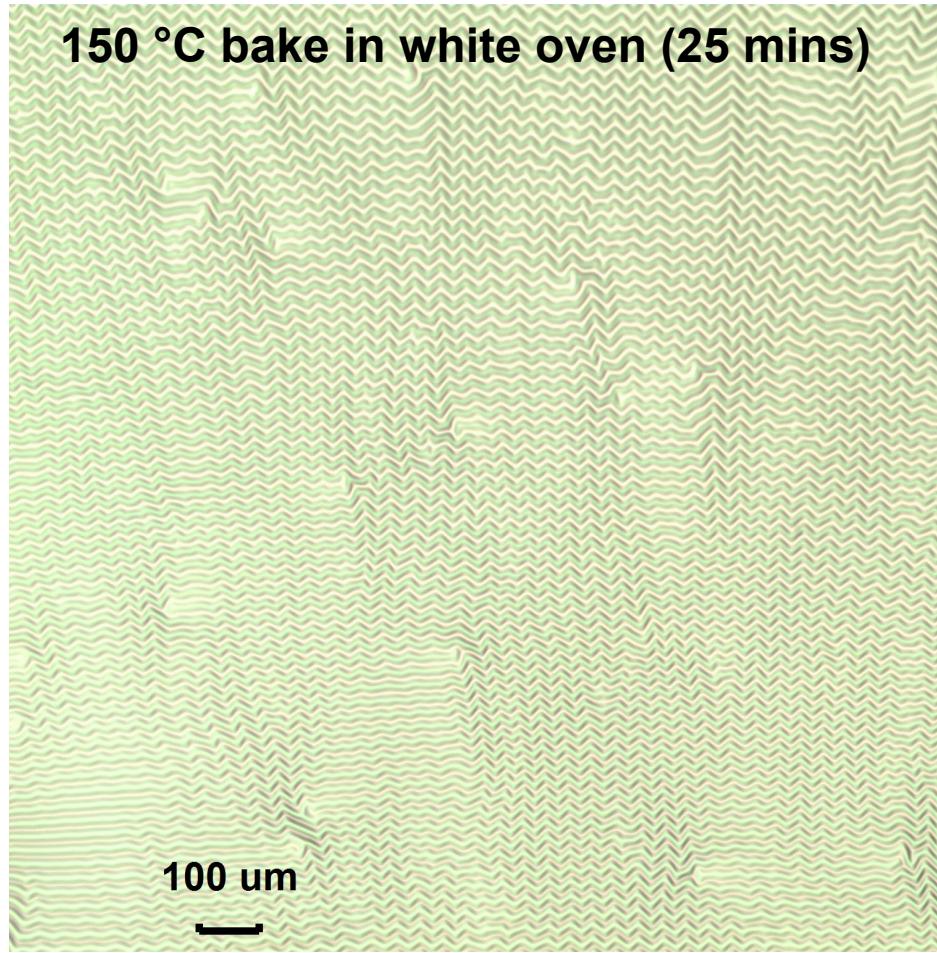

# Cap Pads on PDMS – 3<sup>rd</sup> Try

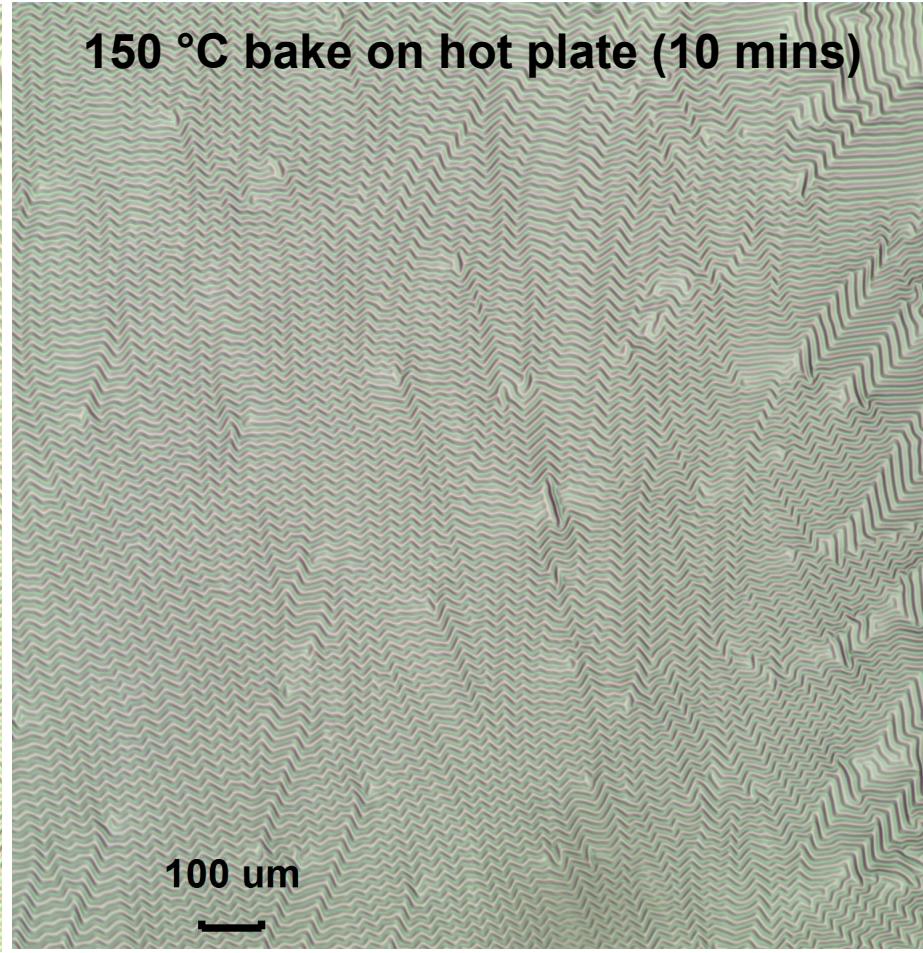

150 °C bake in white oven (25 mins)

150 °C bake on hot plate (10 mins)

- PMGI spun on at 3000 rpm

- 150 °C bake in white oven (25 mins) or on hot plate (10 mins)

# Cap Pads on PDMS – 4<sup>th</sup> Try

- No LOR – only SPR 3612 + 25 min bake in 90 °C oven

- Resist did not adhere well to PDMS – will need HMDS treatment

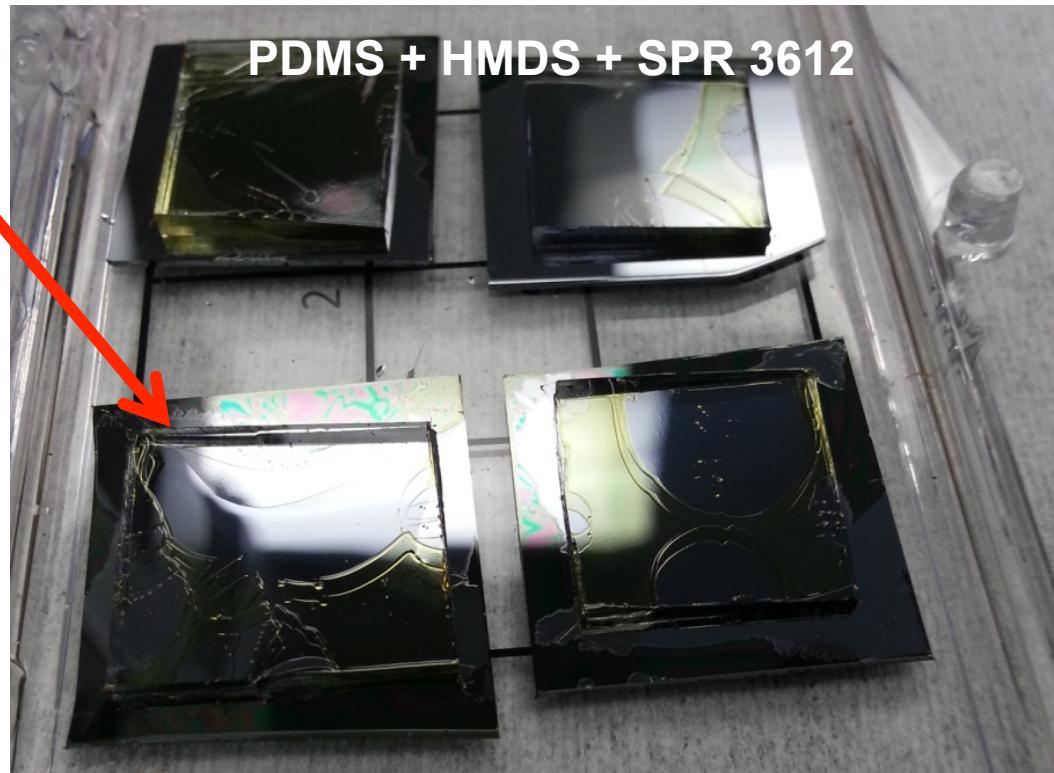

# Photoresist and PDMS

- HMDS does not help with resist adhesion to PDMS.

- Deposited 100 cycles of ALD oxides prior to lithography.

✓ SPR 3612 much easier to spin on (without HMDS) to PDMS/high- $\kappa$ .

- Possible alternative: spin on LOR and bake in the White oven at 100 °C for at least 4 hours before continuing with SPR 3612 and lithography.

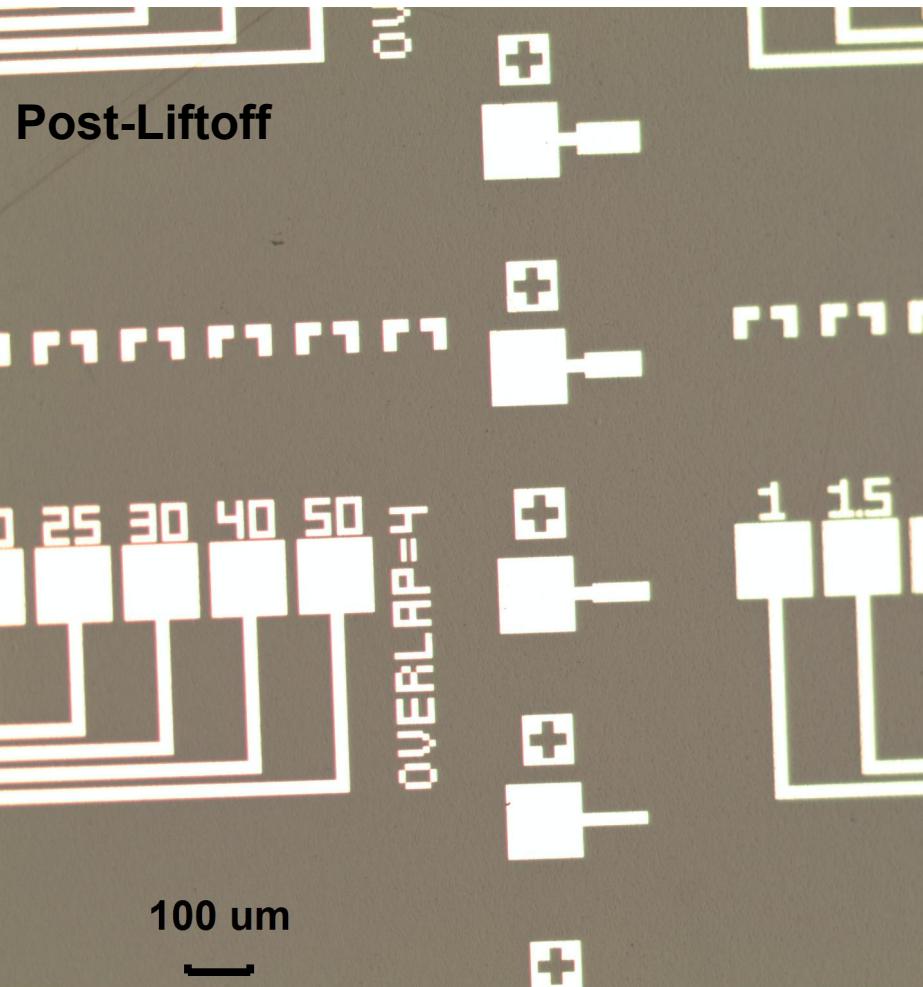

# PDMS + High- $\kappa$ Buffer Layer

150 °C: PDMS/ $\text{Al}_2\text{O}_3$ /Ti/Au/ $\text{Al}_2\text{O}_3$

150 °C: PDMS/ $\text{HfO}_2$ /Ti/Au

post-liftoff

100  $\mu\text{m}$

- Wrinkles visible on metal for 150 °C oxides.

- Also happens for 125 and 100 °C oxides.

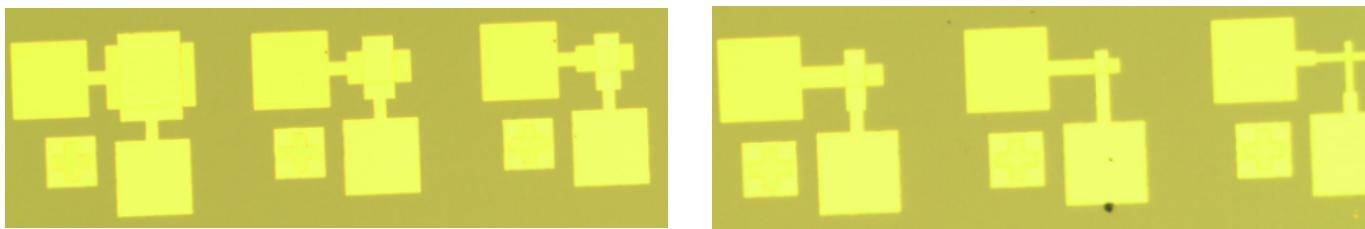

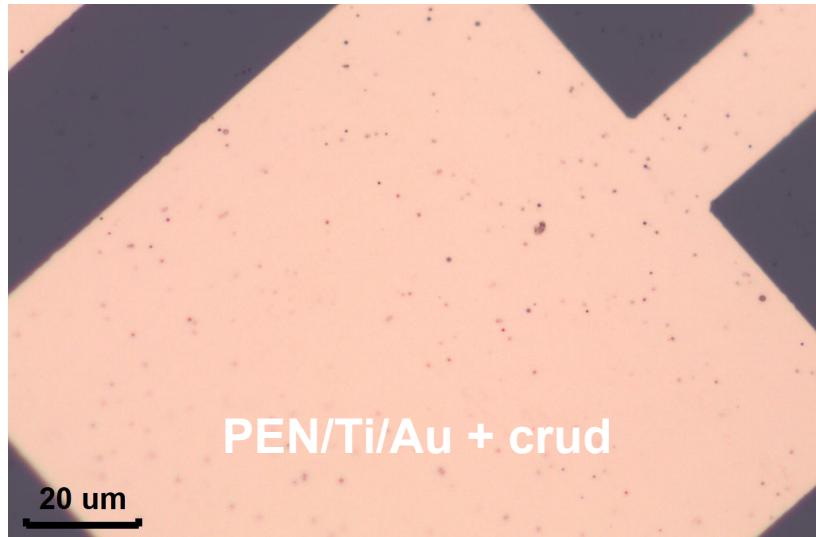

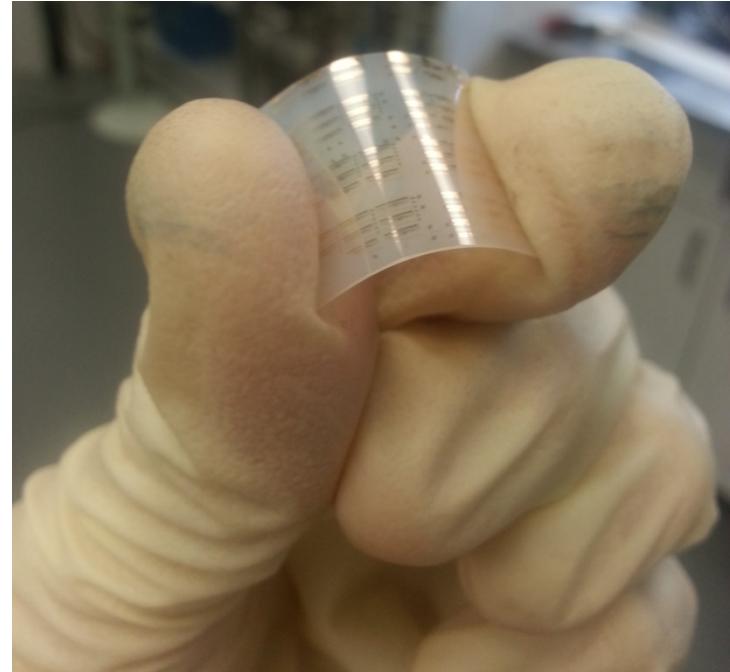

# Cap Pads on PEN (polyethylene naphthalate)

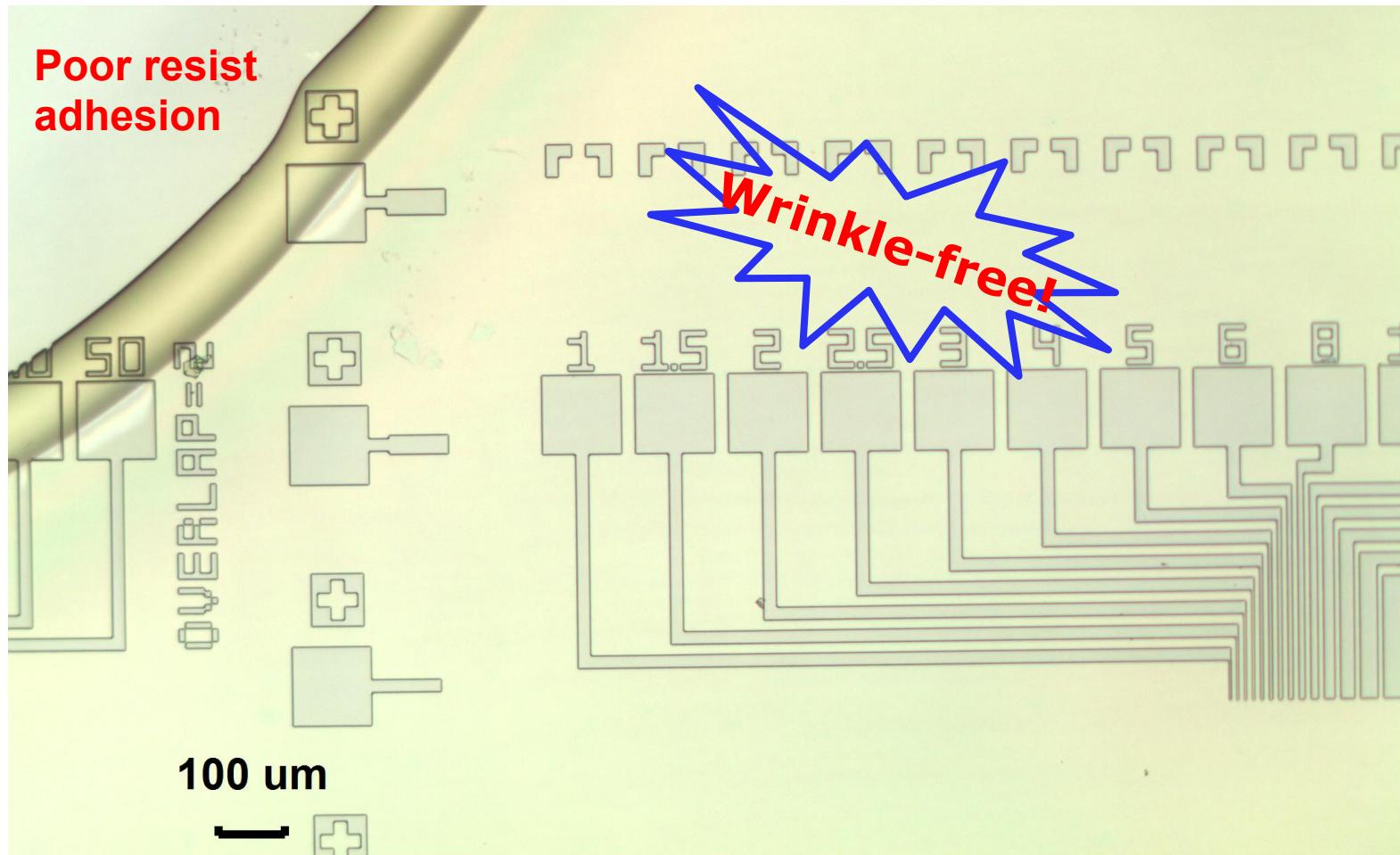

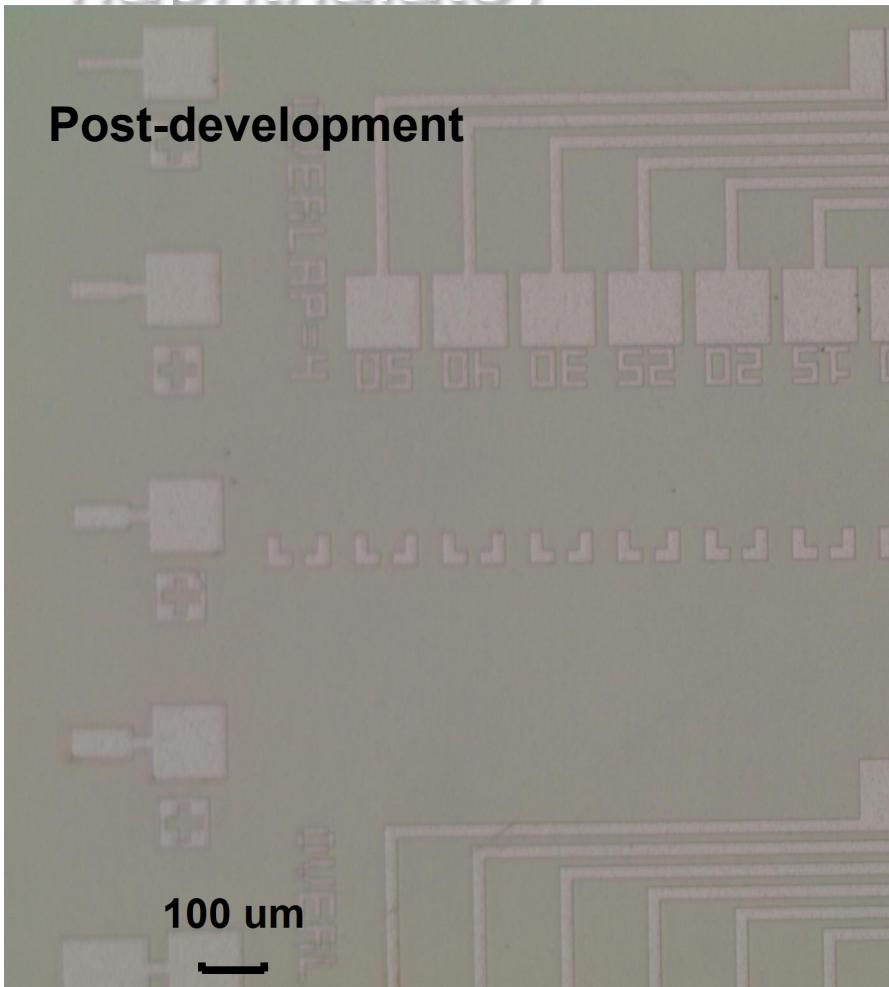

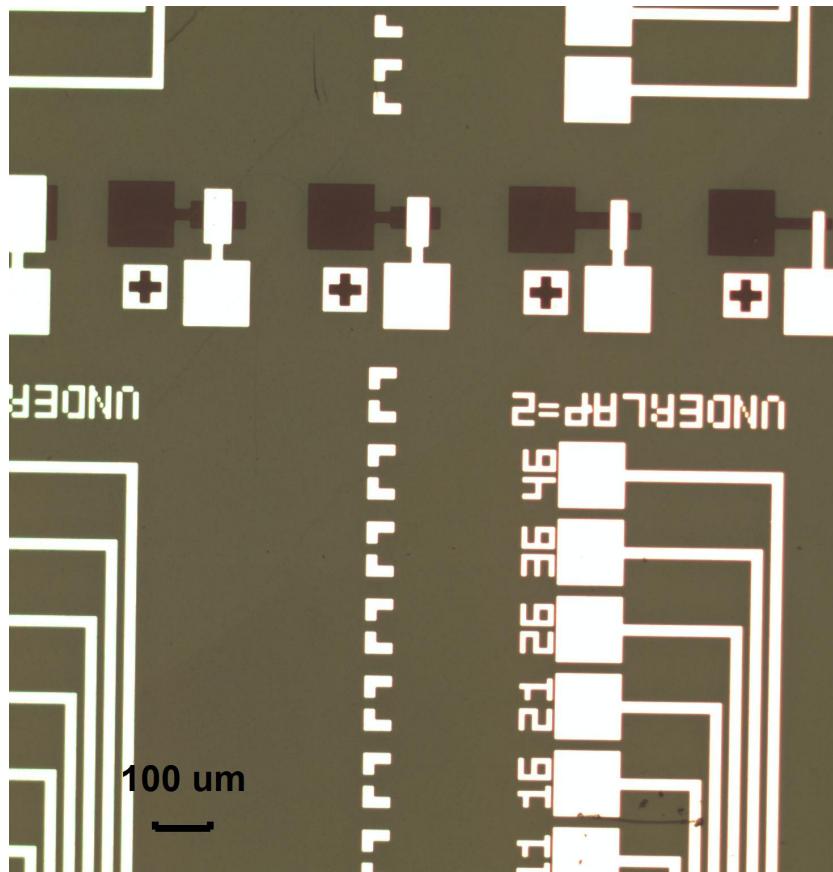

Post-development

- PMGI spun on at 3000 rpm + 150 °C bake on hot plate (10 mins)

- SPR 3612 spun on at 5000 rpm + 90 °C bake on hot plate

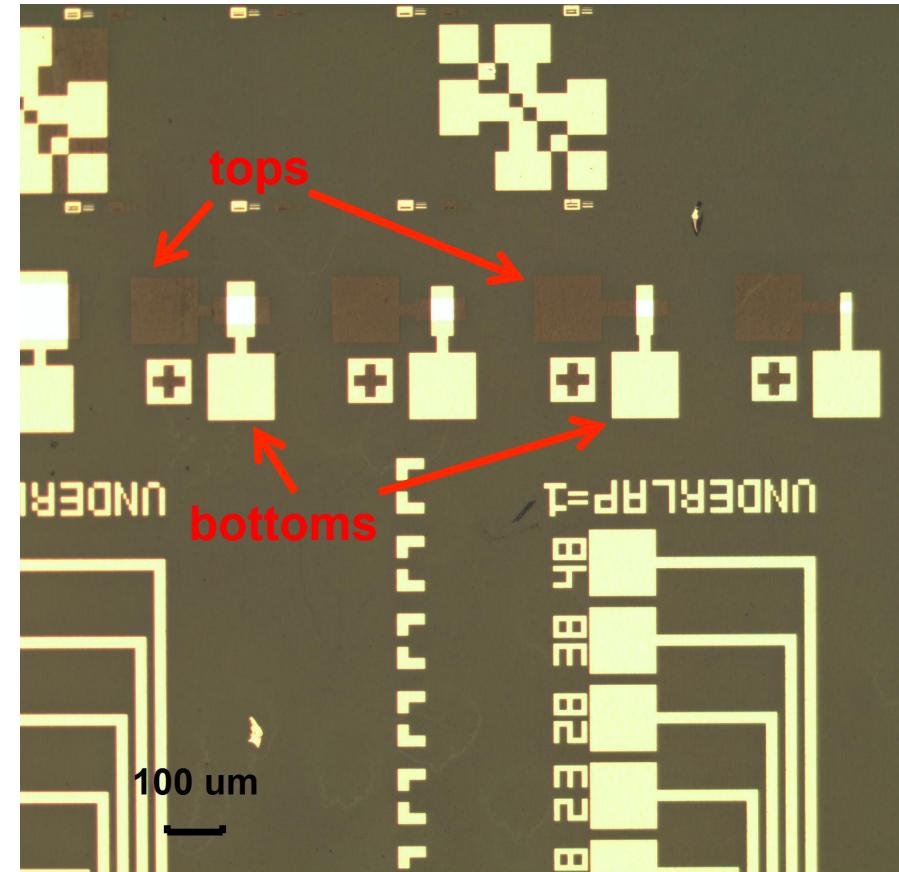

# Caps on PEN – 100 °C MVD Oxides

100 °C: PEN/Ti/Au/Al<sub>2</sub>O<sub>3</sub>/Ti/Au

post-liftoff

100 °C: PEN/Ti/Au/HfO<sub>2</sub>/Ti/Au

post-liftoff

- No cracks after metallization!

- Similar to PDMS, Au did not stick to Ti.

# Caps on PEN – Other Processing Issues

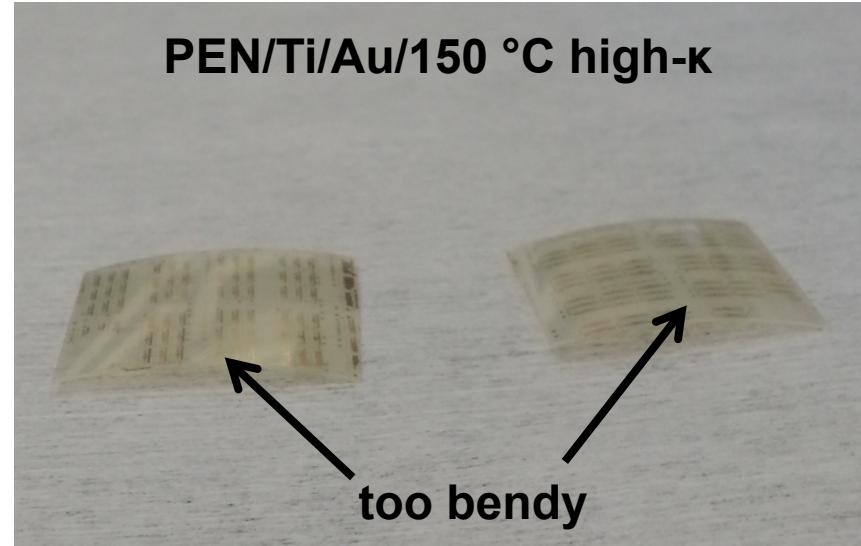

- 10 mins on 150 °C hotplate is fine, but an hour at 150 °C in the MVD causes plastic deformation of PEN. The Headway is consequently unable to achieve vacuum. Resist gluing and kapton tape do not work to fasten it to a carrier wafer.

- ALD oxides deposited at 125 °C cause some bending, but substrates are still spinnable in the Headway. Alignment is very tricky, however. A quartz suppression wafer will be used in the future.

# Observations - Processing on PDMS & PEN

- Films of any kind on PDMS do not fare well above 100 °C.

- An initial layer of high- $\kappa$  oxide is essential for resist adhesion, and helps prevent crud from sticking to the surface.

- It is beneficial to forgo LOR and sonicate during liftoff to minimize the thermal budget.

- Optical resist must be cured in the 90 °C oven.

- PDMS is a sub-optimal substrate for device processing

- PEN acquires an irreversible bend if processed for long at elevated temperatures ( $\geq 150$  °C), but remains flat at 125 °C.

- Off-the-shelf PEN is very dirty, rough, and has scars. Microelectronics grade PEN is recommended for devices.

- PEN is much more robust to thermal expansion and processing abuse than PDMS.

# Conclusions and Future Work

## Observations

- Savannah and MVD oxides show very similar characteristics.

- ALD  $\text{Al}_2\text{O}_3$  ( $\text{HfO}_2$ ) is a stable process down to 125 °C (100 °C).

- PDMS is very tricky for lithography due to stickiness, thermal expansion, and hydrophobicity.

- PEN is an alternative substrate that is much easier to work with.

## Immediate Future Work

- Order microelectronics grade PEN.

- Fabricate caps with 125 °C oxides in MVD.

- Continue to smooth out processing issues.

# Thanks for listening!

**Many thanks are due to Dr. Howe, Dr. Rincon, and Dr. Chen for training, guidance, and support!**

# Backup Slides

# Process Flow - Details

- Begin with clean  $\text{SiO}_2/\text{Si}$  wafer pieces

## Lithography:

- PMGI SF6 @ 3000 rpm for 60 seconds + hotplate

- SPR 3612 @ 5000 rpm for 40 seconds + 90 °C hotplate

- Define bottom electrode with KarlSuss

- Develop for 45 seconds

## Metallization:

- Ebeam evaporate 2/38 nm Ti/Au

- Soak in Remover PG for 3 hours

- Spray with acetone, IPA

- Sonicate if necessary

# Process Flow - Details

- Precondition ALD chamber with recipe to be used

- O<sub>2</sub> plasma in MRC: 20 mTorr, 20 sccm, 50 W, 2 mins

- Immediately transfer chips to ALD chamber, deposit oxide

- FGA in AllWin\_r and fit thickness with Woollam

- Repeat lithography for top electrode

- Repeat metallization for top electrode

- Measure devices

# Savannah - 200 °C Alumina, FGA

**C vs. A**

- $C = 0.703 \pm 0.060$

- $0.677 \pm 0.037 \mu\text{F}/\text{cm}^2$

- $R^2 = 0.998, 0.998$

- $d = 10.0 \text{ nm}$

- $\kappa = 7.94 \pm 0.68, 7.65 \pm 0.42$

note:  $\kappa$  values change by <1% for  $\pm 1 \text{ V}_{\text{DC}}$

**$I_{\text{Leak}}$  vs.  $V_{\text{DC}}$**

- $I_{\text{Leak}} \sim \text{nA}$

- $V_{\text{BD,soft}} \sim 3.5 \text{ V}$

- $E_{\text{crit,hard}} \sim 0.35 \text{ V/nm}$

- $V_{\text{BD,soft}} \sim 7.5 \text{ V}$

- $E_{\text{crit,soft}} \sim 0.75 \text{ V/nm}$

# Savannah - 200 °C Alumina, O<sub>2</sub> anneal

**C vs. A**

- $C = 0.662 \pm 0.021$

- $0.679 \pm 0.009 \mu\text{F}/\text{cm}^2$

- $R^2 = 0.999, 1.000$

- $d = 10.0 \text{ nm}$

- $\kappa = 7.48 \pm 0.23, 7.67 \pm 0.10$

**I<sub>Leak</sub> vs. V<sub>DC</sub>**

- $I_{\text{Leak}} \sim nA$

- $V_{\text{BD,soft}} \sim 3.5 \text{ V}$

- $E_{\text{crit,hard}} \sim 0.35 \text{ V/nm}$

- $V_{\text{BD,soft}} \sim 7.8 \text{ V}$

- $E_{\text{crit,soft}} \sim 0.78 \text{ V/nm}$

# Savannah - 200 °C Hafnia, FGA

**C vs. A**

**$I_{\text{Leak}}$  vs.  $V_{\text{DC}}$**

- $C = 1.60 \pm 0.007$

- $1.61 \pm 0.004 \mu\text{F}/\text{cm}^2$

- $R^2 = 1.000, 1.000$

- $d = 8.7 \text{ nm}$

- $\kappa = 15.70 \pm 0.07, 15.84 \pm 0.04$

- $I_{\text{Leak}} \sim \text{nA}$

- $V_{\text{BD}} \sim 3.2 \text{ V}$

- $E_{\text{crit}} \sim 0.37 \text{ V/nm}$

# Savannah - 200 °C Hafnia, O<sub>2</sub> anneal

**C vs. A**

**I<sub>Leak</sub> vs. V<sub>DC</sub>**

- $C = 1.59 \pm 0.011$

- $1.42 \pm 0.014 \mu\text{F}/\text{cm}^2$

- $R^2 = 1.000, 1.000$

- $d = 8.7 \text{ nm}$

- $\kappa = 15.59 \pm 0.11, 13.95 \pm 0.14$

- $I_{\text{Leak}} \sim \text{nA}$

- $V_{\text{BD}} \sim 3.2 \text{ V}$

- $E_{\text{crit}} \sim 0.37 \text{ V/nm}$

# Savannah - 100 °C Hafnia, 150 °C FGA

**C vs. A**

- $C = 1.20 \pm 0.03$

- $1.10 \pm 0.01 \mu\text{F}/\text{cm}^2$

- $R^2 = 1.000, 1.000$

- $d = 11.9 \text{ nm}$

- $\kappa = 16.2 \pm 0.4, 14.8 \pm 0.1$

**$I_{\text{Leak}}$  vs.  $V_{\text{DC}}$**

- $I_{\text{Leak}} \sim \text{nA}$

- $V_{\text{BD}} > 6.0 \text{ V}$

- $E_{\text{crit}} \sim 0.50 \text{ V/nm}$

# MVD - 125 °C Alumina + 125 °C FGA

**C vs. A**

- $C = 0.762 \pm 0.001 \mu\text{F}/\text{cm}^2$

- $R^2 = 1.000$

- $d \approx 8.9 \text{ nm}$

- $\kappa \approx 7.7 \pm 0.02$

**$I_{\text{Leak}}$  vs.  $V_{\text{DC}}$**

- $I_{\text{Leak}} < \text{nA}$

- $V_{\text{BD}} > 3.0 \text{ V}$

- $E_{\text{crit}} \sim 0.34 \text{ V/nm}$

# MVD - 100 °C Hafnia + 100 °C FGA

**C vs. A**

- $C = 1.33(4) \pm 0.004$

- $1.30(7) \pm 0.003 \mu\text{F}/\text{cm}^2$

- $R^2 = 1.000, 1.000$

- $d = 11.3 \text{ nm}$

- $\kappa = 17.03 \pm 0.0(5), 16.6(9) \pm 0.03$

**$I_{\text{Leak}}$  vs.  $V_{\text{DC}}$**

- $I_{\text{Leak}} < \text{nA}$

- $V_{\text{BD}} > 5.5 \text{ V}$

- $E_{\text{crit}} \sim 0.49 \text{ V/nm}$

# First PDMS Thickness Experiments

- Si wafer – 500 rpm for 30 s

- $\mu = 0.75 \text{ mm}$ ,  $\sigma = 0.06 \text{ mm}$

- Si wafer – 500 rpm for 15 s

- $\mu = 0.79 \text{ mm}$ ,  $\sigma = 0.02 \text{ mm}$

- Si wafer – 100 rpm for 15 s

- Could not accurately measure

- Pyrex dish – let sit

- $\mu = 3.67 \text{ mm}$ ,  $\sigma = 0.52 \text{ mm}$

- Could not remove from mold

- Fluoroware lid – let sit

- $\mu = 3.46 \text{ mm}$ ,  $\sigma = 0.16 \text{ mm}$

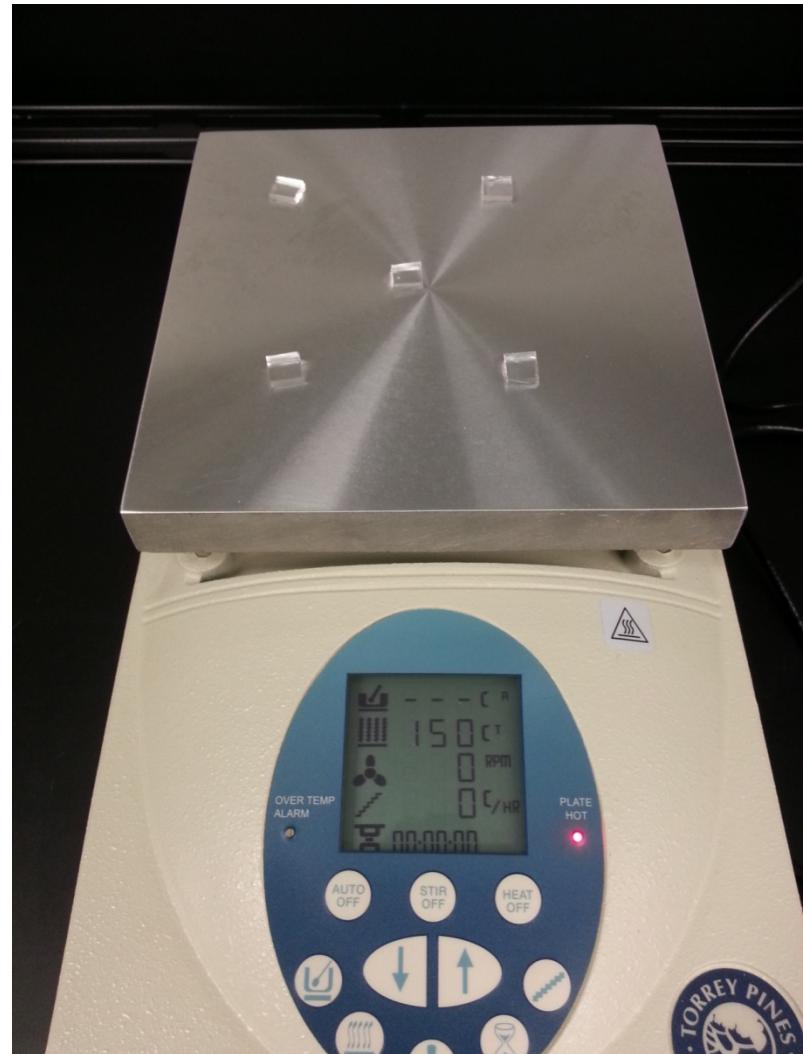

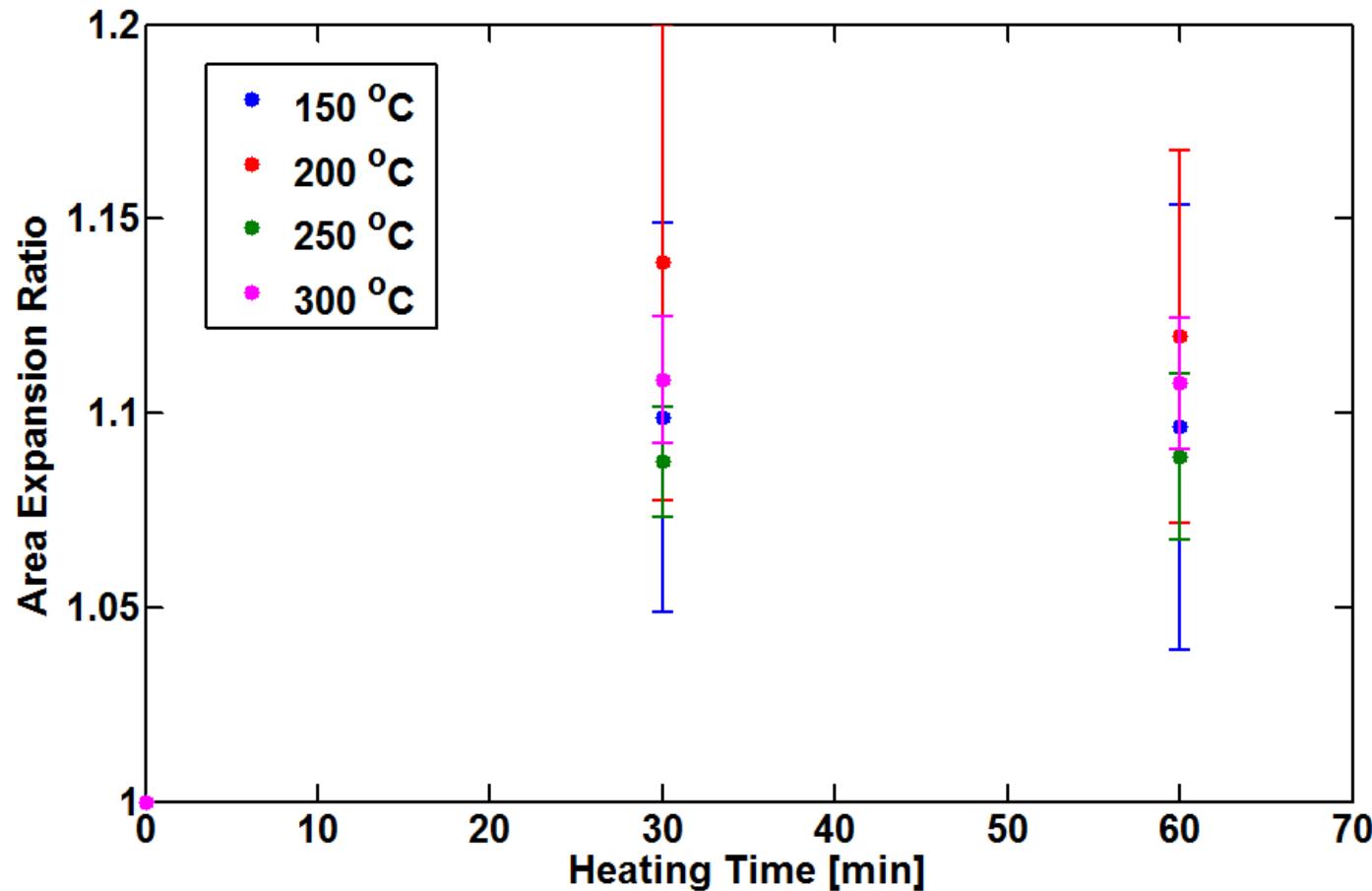

# PDMS Thermal Integrity

- Five squares approximately  $10 \times 10 \text{ mm}^2$  were cut and heated.

- Height and width were measured with calipers at 30 and 60 minutes of heating for various temperatures.

- PDMS was fine up through an hour at 300 °C.

# PDMS Thermal Integrity

- Data points → average area ratio

- Error bars → one standard deviation

- PDMS also able to withstand 300 °C H<sub>2</sub>/Ar anneal for 1 hour